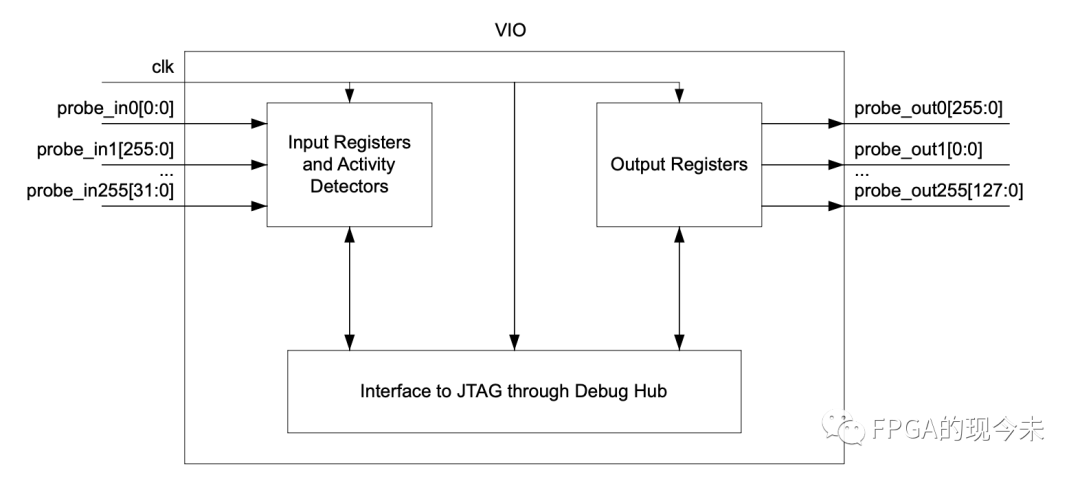

和FPGA设计进行连接。由于VIO核与被监视和驱动的设计同步,因此应用于设计的时钟约束也适用于VIO核内的元件。当使用这个核进行实时交互时,需要使用Vivado逻辑分析特性。 接下来将介绍

2021-09-23 16:11

在Vivado中,VIO(Virtual Input/Output)是一种用于调试和测试FPGA设计的IP核,它允许设计者通过JTAG接口实时读取和写入FPGA内部的寄存器,从而检查设计的运行状态并修改其行为。VIO

2025-06-09 09:32

一般情况下ILA和VIO都是用在chipscope上使用,VIO可以作为在chipscope时模拟IO。

2022-06-12 15:51

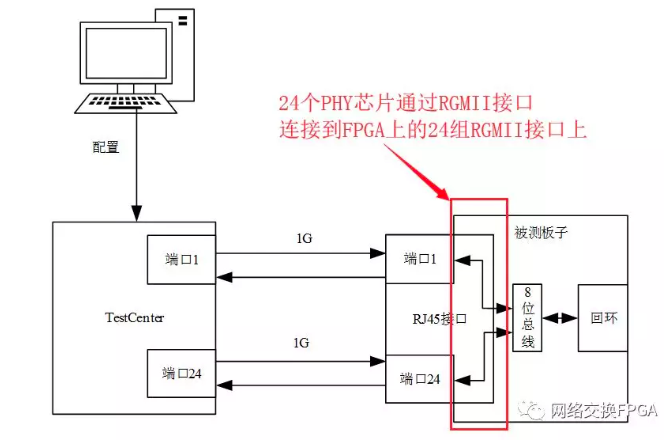

实验室回来一批板子,上面有RGMII接口、SGMII接口等各种接口,怎么测试这些网口是否正常呢?的确需要一些经验。比如RGMII接口,最重要的是看在哪里去做的时钟和数据偏移。这时,常常需要使用VIO

2020-11-06 13:06

电压比较器VIO的开环测试 输入失调电压(VIO)是电压比较器(以下简称比较器)一个重要的电性能参数,GB/T 6798-1996中,将其定义为“使输出电压为规定

2010-01-15 17:57

信号线设置成类似于CPU总线的结构,监测计数器或者状态寄存器编成相应的地址,轮询读取回PC,在PC上通过TCL或者其它语言捕获数据。甚至可以将多个FPGA芯片都通过VIO进行调试,远程操作,效率也可以大大提升。另外,也可以设置专门的测试帧,在里面打各种不同大小的闭

2019-07-19 10:19

vivado有project模式和non-project模式,project模式就是我们常用的方式,在vivado里面新建工程,通过GUI界面去操作;non-project模式就是纯粹通过tcl来指定

2022-10-17 10:09

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado

2018-07-04 11:23

Vivado综合默认是timing driven模式,除了IO管脚等物理约束,建议添加必要的时序约束,有利于综合逻辑的优化,同时综合后的design里面可以评估时序。

2023-07-03 09:03

在以往的项目中,要控制FPGA内部某个信号的值,往往是通过配置寄存器来实现的。其实Xilinx还提供了一个叫VIO的core,可以动态改变FPGA内部某个信号的值,但是一直没有用过,一来对于以前的项目来说,没有应用场景,通过寄存器就可以配置了;二来感觉这个东西不是很“实用”。

2023-12-11 18:26