和FPGA设计进行连接。由于VIO核与被监视和驱动的设计同步,因此应用于设计的时钟约束也适用于VIO核内的元件。当使用这个核进行实时交互时,需要使用Vivado逻辑分析特性。 接下来将介绍

2021-09-23 16:11

在Vivado中,VIO(Virtual Input/Output)是一种用于调试和测试FPGA设计的IP核,它允许设计者通过JTAG接口实时读取和写入FPGA内部的寄存器,从而检查设计的运行状态并修改其行为。VIO

2025-06-09 09:32

一般情况下ILA和VIO都是用在chipscope上使用,VIO可以作为在chipscope时模拟IO。

2022-06-12 15:51

只能识别一条Chain(User0)。所以,如果要同时在analyzer里面使用ILA(看波形)和VIO会不太现实(需要自己手动例化ILA Core和连接需要看的信号)。但是通过TCL可以访问所有

2012-03-08 15:29

你好,我从Digilent购买了一块ZYBO板,并兑换了Vivado Design Suite附带的优惠券。今天我试图实例化一个VIO核心,我的许可证出错了。如何访问Vivado Analyzer

2018-12-14 11:35

请问VIO输出的控制信号的类型该如何设置?如图有三种类型分别是什么意思

2019-04-27 15:50

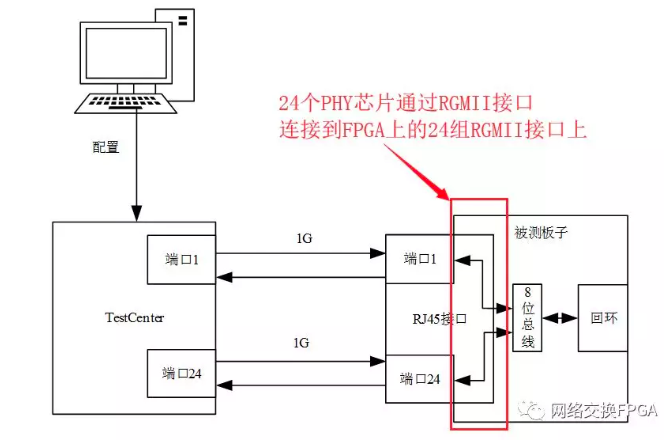

实验室回来一批板子,上面有RGMII接口、SGMII接口等各种接口,怎么测试这些网口是否正常呢?的确需要一些经验。比如RGMII接口,最重要的是看在哪里去做的时钟和数据偏移。这时,常常需要使用VIO

2020-11-06 13:06

电压比较器VIO的开环测试 输入失调电压(VIO)是电压比较器(以下简称比较器)一个重要的电性能参数,GB/T 6798-1996中,将其定义为“使输出电压为规定

2010-01-15 17:57

信号线设置成类似于CPU总线的结构,监测计数器或者状态寄存器编成相应的地址,轮询读取回PC,在PC上通过TCL或者其它语言捕获数据。甚至可以将多个FPGA芯片都通过VIO进行调试,远程操作,效率也可以大大提升。另外,也可以设置专门的测试帧,在里面打各种不同大小的闭

2019-07-19 10:19

在vivado里面仿真时出现这个是什么原因啊[VRFC 10-2063] Modulenot found while processing module instance["C

2019-09-22 09:23