和FPGA设计进行连接。由于VIO核与被监视和驱动的设计同步,因此应用于设计的时钟约束也适用于VIO核内的元件。当使用这个核

2021-09-23 16:11

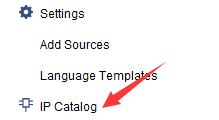

大家好,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。 首先咱们来了解一下vivado的IP核,IP

2018-05-28 11:42

今天介绍的是vivado的三种常用IP核:时钟倍频(Clocking Wizard),实时仿真(ILA),ROM调用(Block Memory)。

2023-02-02 10:14

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

2018-12-22 14:26

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等

2021-04-27 15:45

Modelsim是十分常用的外部仿真工具,在Vivado中也可以调用Modelsim进行仿真,下面将介绍如何对vivado进行配置并调用Modelsim进行仿真,在进行

2023-07-24 09:04

在linux系统上实现vivado调用VCS仿真教程 作用:vivado调用VCS仿真可以加快工程的仿真和调试,提高效率。 前期准备:确认安装

2018-07-05 03:30

.coe格式的数据文件简介 在Vivado中,对rom进行初始化的文件是.coe文件.它的格式如下: memory_initialization_radix=10

2020-11-20 15:01

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言

2017-02-08 13:08

,发现Modelsim10.5的版本也是可以使用的。笔者尝试过Modelsim10.4,发现该版本不支持。所以需要使用Vivado2017.3来调用Modelsim的工程师,需要选择正确的Modelsim版本。否者将调用

2019-03-30 09:51