在linux系统上实现vivado调用VCS仿真教程 作用:vivado调用VCS仿真可以加快工程的仿真和调试,提高效率。 前期准备:确认安装

2018-07-05 03:30

,发现Modelsim10.5的版本也是可以使用的。笔者尝试过Modelsim10.4,发现该版本不支持。所以需要使用Vivado2017.3来调用Modelsim的工程师,需要选择正确的Modelsim版本。否者将调用

2019-03-30 09:51

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

2018-12-22 14:26

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到时钟向导IP,下面就介绍一下在vivado中进行PL开发时调用IP的方法。

2018-12-22 15:14

双口RAM概述 双口RAM(dual port RAM)在异构系统中应用广泛,通过双口RAM,不同硬件架构的芯片可以实现数据的交互,从而实现通信。

2018-03-21 13:34

在同步的 Rust 方法中调用异步代码经常会导致一些问题,特别是对于不熟悉异步 Rust runtime 底层原理的初学者。

2023-12-24 16:23

下面是调用的DDR3模块的,模块的倒数第二行是,模块的时钟输入,时钟源来自PLL产生的系统时钟的倍频。

2025-05-03 10:21

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado

2018-07-04 11:23

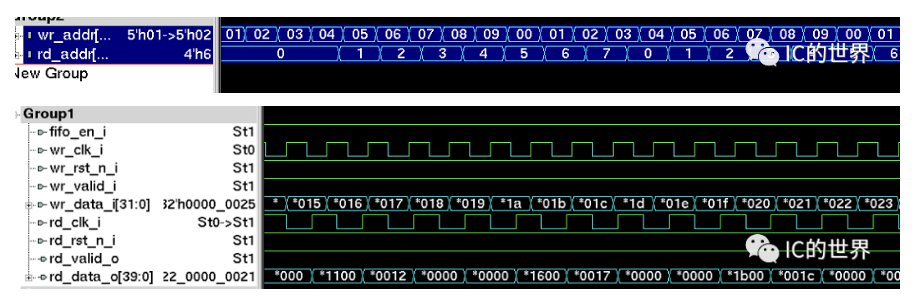

在进行模块设计时,我们经常需要进行数据位宽的转换,常见的两种转换场景有同步时钟域位宽转换和异步时钟域位宽转换。本文将介绍异步时钟域位宽转换

2023-11-23 16:41

由目标运动引起的运动变化区域包括运动目标在前后两帧中的共同位置(图中黑色区域)、在当前帧中新显露出的背景区域和新覆盖的背景区域三部分。

2018-04-20 20:26