Vivado时钟的两大特性--时钟延迟和时钟的不确定性。

2017-11-17 11:38

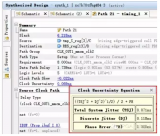

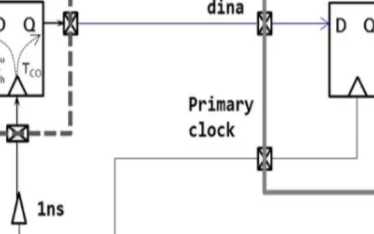

数字设计中,“时钟”表示在寄存器间可靠地传输数据所需的参考时间。Vivado的时序引擎通过时钟特征来计算时序路径需求,通过计算裕量(Slack)的方法报告设计时序空余。时钟

2022-04-20 10:40

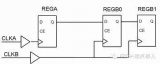

该视频演示了如何使用Vivado IP Integrator组装具有多个时钟域的设计。 它显示了Vivado中的设计规则检查和功能如何帮助用户自动执行此流程。

2018-11-27 07:40

使用“时钟校准去歪斜”时,在 Vivado 中会显示下列消息以指明是否启用该功能特性

2023-07-07 14:14

但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

2022-02-16 16:21

在Vivado中禁止自动生成BUFG(Buffered Clock Gate)可以通过以下步骤实现。 首先,让我们简要了解一下什么是BUFG。BUFG是一个时钟缓冲器,用于缓冲输入时钟信号,使其更稳

2024-01-05 14:31

在Vivado中通过set_clock_groups来约束不同的时钟组,它有三个选项分别是-asynchronous,-logically_exclusive

2017-02-08 08:39

提出了一个基于虚拟时钟指数逼近的无线传感器网络时钟同步协议,采用一个虚拟时钟作为全网同步的基础,从而实现全网同步。由于采

2015-08-18 15:27

Vivado 的XDC设置输出延时 Vivado 的XDC设置输出延时,用于输出伴随时钟和数据的,数据是由系统时钟125M驱动,伴随

2021-06-09 17:28

时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。 这次

2019-09-15 16:38