作者:Mculover666 1.实验目的 用HDL语言+Vivado创建一个挂载在AXI总线上的自定义IP核 2.实验步骤 2.1.创建一个新的项目 2.2.

2020-12-21 16:34

自定义sobel滤波IP核 IP接口遵守AXI Stream协议

2019-08-06 06:04

大家好,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。 首先咱们来了解一下vivado的

2018-05-28 11:42

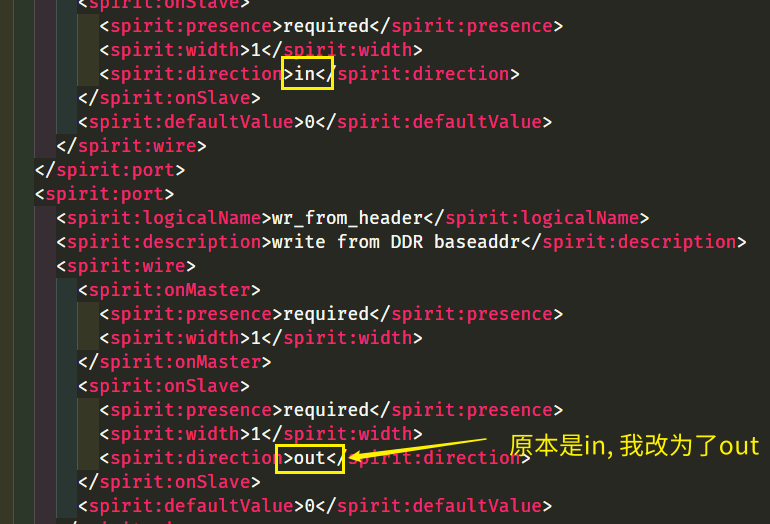

因为 BD 中连线太多,所以想自定义下 interface 简化连线,定义好了一个 interface,但当准备在自定义 IP 中指定它时,发现我把一个信号的方向搞错了

2022-08-02 09:49

在FPGA实际的开发中,官方提供的IP并不是适用于所有的情况,需要根据实际修改,或者是在自己设计的IP时,需要再次调用时,我们可以将之前的设计封装成自定义

2022-04-21 08:58

今天介绍的是vivado的三种常用IP核:时钟倍频(Clocking Wizard),实时仿真(ILA),ROM调用(Block Memory)。

2023-02-02 10:14

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整

2023-06-25 16:31

在用Vivado制作自己的IP的时候,已经熟悉了将功能关联的一组port组合成一个interface,比如这个M_AXIS: 这样可以简化框图设计中IP的显示, 方便连线、优化框图设计布局。 但一般

2017-02-08 11:50

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

2018-12-22 14:26

SOPC中自定义外设和自定义指令性能分析 NiosII是一个建立在FPGA上的嵌入式软核处理器,灵活性很强。作为体现NiosII灵活性精髓的两个最主要方面,自

2009-03-29 15:12