随着FPGA规模的增大,设计复杂度的增加,Vivado编译时间成为一个不可回避的话题。尤其是一些基于SSI芯片的设计,如VU9P/VU13P/VU19P等,布局布线时间更是显著增加。当然,对于一些设计而言,十几个小时

2024-09-18 10:43

在Vivado Implementation阶段,有时是有必要分析一下什么原因导致运行时间(runtime)过长,从而找到一些方法来缩短运行时间。

2019-05-29 14:37

建立时间和保持时间是SOC设计中的两个重要概念。它们都与时序分析有关,是确保芯片正常工作的关键因素。

2023-08-23 09:44

在ISE下,对综合后的网表进行编辑几乎是不可能的事情,但在Vivado下成为可能。Vivado对Tcl的支持,使得Tcl脚本在FPGA设计中有了用武之地。本文通过一个实例演示如何在

2017-11-18 03:16

在Vivado Design Suite中,Vivado综合能够合成多种类型的属性。在大多数情况下,这些属性具有相同的语法和相同的行为。

2019-05-02 10:13

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够

2020-01-28 17:34

我们使用 Vivado ®Design Suite 的高层次综合 (HLS) 工具来评估针对 E-UTRA I/Q 数据的开放无线电设备接口 (ORI) 标准压缩方案,以估计其对信号保真度的影响、造成的时延及其实现成本。我们发现赛灵思的

2018-07-24 09:30

虽然想必您知道,在综合或实现阶段,增量运行可以从参考文件中读取和复制信息,但仅在某些阶段中能节省时间,如果网表发生大量更改,其中引用的内容就会减少,编译时间也会受到相应影响。

2023-10-09 16:48

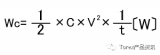

输出电压保持时间是指当电源回路的输入部被停止供电后,输出电压的保持时间。微处理器或RAM等的Backup电路也是电压保持

2018-08-01 09:19

理由一:突破器件密度极限:在单个器件中更快速集成更多功能;理由二:Vivado以可预测的结果提供稳健可靠的性能和低功耗;理由三:Vivado设计套件提供了无与伦比的运行时间和存储器利用率;理由四:使用

2017-11-22 08:15