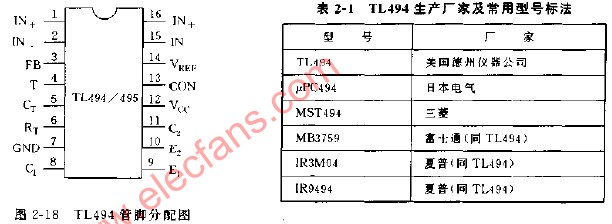

TL494管脚分配图

2009-10-14 16:21

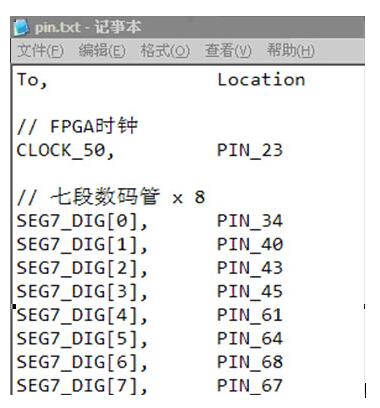

将Quartus II中FPGA管脚的分配及保存方法做一个汇总。本文首先介绍了FPGA 的管脚分配方法,其次介绍了Quartus II自动添加

2018-05-16 11:44

在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从

2017-11-25 07:38

设计过FPGA的原理图,看FPGA的手册,说管脚的分配问题,如时钟管脚要用GC类管脚,而且单端时钟输入时要用P类型的管脚

2017-02-11 03:48

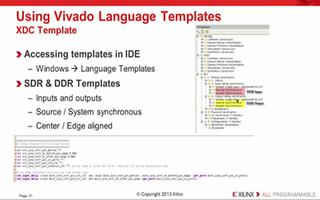

在Vivado中新建IO Planning工程来初步引脚分配,这样会大大提高开发效率 在这里,你可以选择最右侧的开发板型号,也可以选择Part,具体的FPGA的型号,选择完后,我们可以很清晰的看到该型号的资源列表:包括IO数、可用的IO数、内部BRAM大小、时钟

2018-10-22 17:12

Spartan-6系列具有低成本、省空间的封装形式,能使用户引脚密度最大化。所有Spartan-6 LX器件之间的引脚分配是兼容的,所有Spartan-6 LXT器件之间的引脚分配是兼容的,但是Spartan-6 LX和Spartan-6 LXT器件之间的引脚

2018-07-01 10:48

Xilinx Vivado开发环境编译HDL时,对时钟信号设置了编译规则,如果时钟由于硬件设计原因分配到了普通IO上,而非_SRCC或者_MRCC专用时钟管脚上时,编译器就会提示错误。

2024-04-15 11:38

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado

2018-07-04 11:23

这个培训将会深度介绍适于Xililnx 可编程门阵列的HDL代码风格, 产生和验证时序约束的正确方法, 和如何利用分析和布局规划工具分配时钟和管脚,产生物理约束以达到最大设计性能. 对于初次从事FPGA设计或使用Vivado

2018-05-23 15:47

前面一篇介绍了从新建工程一直到编写代码进行行为仿真,这篇继续进行介绍。 修改器件型号 新建工程时选择过器件型号,如果新建好工程后需要修改型号,可以选择菜单Tools - Project Settings。 弹出窗口中,点击Project Device右侧的按钮,即可选择器件型号。 综合(Synthesis) 综合类似于编程中的编译。 在Flow Navigator或Flow菜单中,选择Synthesis - Run Synthesis;或点击工具栏中的三角形按钮如图,即可开始对设计文件进行综合。 综合以及后面的实现等操作,耗

2017-02-08 12:56