最近有些朋友在ISE中做的V7项目需要切换到vivado来,但导入代码后,导入约束时,发现vivado不再支持UCF文件,如果手抄UCF约束到

2017-03-24 13:54

Vivado IDE约束管理器将任何已编辑的约束保存回XDC文件中的原始位置,但不会保存在Tcl脚本中。 任何新约束都保存在标记为目标的XDC文件的末尾。

2020-11-13 10:53

提到位置约束,我们会想到手工布局的方式,即画Pblock,将指定模块放入相应Pblock内,这既是面积约束又是位置约束,但显然这种约束是较为具体的位置

2022-11-17 11:47

有时我们对时序约束进行了一些调整,希望能够快速看到对应的时序报告,而又不希望重新布局布线。这时,我们可以打开布线后的dcp,直接在Vivado Tcl Console里输入更新后的时序约束。如果调整

2024-10-24 15:08

1 I/O延迟约束介绍 要在设计中精确建模外部时序,必须为输入和输出端口提供时序信息。Xilinx Vivado集成设计环境(IDE)仅在FPGA边界内识别时序,因此必须使用以下命令指定超出这些边界

2020-11-29 10:01

介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。所以首先要设计合理,

2018-06-25 09:14

《XDC 约束技巧》系列中讨论了XDC 约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入 Viv

2023-05-04 11:20

Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握

2017-11-18 03:52

Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为

2023-04-15 09:43

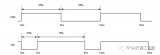

在数字设计中,时钟代表从寄存器(register)到寄存器可靠传输数据的时间基准。

2024-01-04 09:16