使用的是Vivado,希望使用其FIRIP核设计一个滤波器,该滤波器不是固定结构,而是可以根据项目中的变量filterselect的值选择其通带频率,例如filters

2017-08-10 05:49

领域都有着广泛的应用。 Vivado自带的FIR滤波器IP核已经很好用,这里借FIR滤波器的设计,介绍Simulink图形设计编程方法。Simulink可以使设计更直观

2024-04-17 17:29

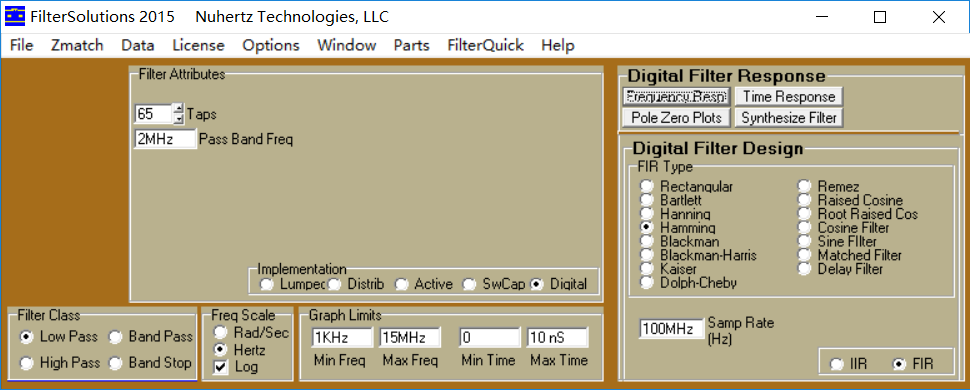

在生成滤波器IP核之前需要产生抽头系数,这个抽头系数的阶数是自己设定的,阶数越高代表滤波器乘累加运算越多,但是阶数大小的选择要看是否满足自己的设计要求(例如衰减db是否满足要求)。同时,生成的

2018-07-06 10:00

FIR(Finite Impulse Response)滤波器:有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响

2024-03-25 09:18

本文使用 DDS 生成三个信号,并在 Vivado 中实现低通滤波器。低通滤波器将滤除相关信号。

2025-03-01 14:31

在Vivado FIR滤波器设计与仿真(一)中产生了两路正弦信号,频率分别为4MHz和5MHz,今天要进行FIR滤波器设计,在进行滤波器设计之前,需要对

2020-12-28 12:57

针对人脸识别应用,提出一种基于学习且具有鉴别能力的核图像微分滤波器。首先,区别于现有滤波器的手工设计方法,该滤波器利用训练集动态学习获得,通过在学习过程中融入线性判别分

2017-12-04 11:28

最近进行FPGA学习,使用FIR滤波器过程中出现以下问题:使用FIR滤波器IP核中,输入数据为1~256,滤波器系数为,coef =-1469,-14299 ,-218

2018-11-02 17:17

本文将简单介绍FIR滤波器的原理,详细介绍使用Verilog HDL设计并行FIR滤波器的流程和方法。接下来几篇会介绍串行结构FIR的Verilog设计、使用Quartus和Vivado的IP

2020-09-25 17:44

滤波器,滤波器电路,滤波器原理 一、概述 1.定义 凡是可以使信号中特定的频率成分通过,而极大地衰减或抑制其他频率成分的装置或

2010-03-24 13:58