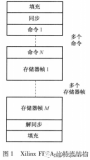

比特流是一个常用词汇,用于描述包含FPGA完整内部配置状态的文件,包括布线、逻辑资源和IO设置。大多数现代FPGA都是基于SRAM的,包括Xilinx Spartan和Virtex系列。在FPGA上

2024-07-16 18:02

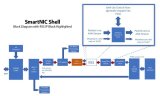

DVK是用于解码器IP设计和合规性验证的比特流和软件工具链。它是芯片RTL设计、目标设备集成(如智能手机、智能电视、机顶盒)、发货给客户前的软件堆栈验证的必备工具。

2022-10-08 11:06

本人需要利用Vivado软件中的DDS核生成一个正弦信号。由于后期还要生成线性调频信号,如果直接编写代码生成比特流文件下载到板子上进行验证会使工作的效率大大下降,所有想利用Vi

2018-07-13 08:32

Vivado IDE约束管理器将任何已编辑的约束保存回XDC文件中的原始位置,但不会保存在Tcl脚本中。 任何新约束都保存在标记为目标的XDC文件的末尾。

2020-11-13 10:53

文件是一个xml格式的文件,它能够搜集ip所有的配置信息,更重要的是包括Vivado指向的ip所生成的大量文件,比如上下文综合、约束和模拟

2018-05-02 08:50

本文对于第一个功能,我们在Vivado设计中不需要包含QSPI接口。我们只需要在Vivado配置中更新对QSPI的设置,提供QSPI Flash存储器与FPGA配置管脚的连接。然而,一旦FPGA配置

2017-12-15 08:14

借鉴参考Vivado之前的布局结果,换言之,我们确定的Pblock位置未必是工具认为的最佳位置。对于特定的底层单元,例如RAMB36K或DSP48,可通过属性LOC指定其具体位

2022-11-17 11:47

大多数FPGA程序员认为,高级工具总是发出更大的比特流,作为提高生产率的 "代价"。但是这总是真的吗?

2023-06-27 10:10

在调试Vivado 过程中,由于生成的BIT文件过大,而我使用的FLASH又是32MBIT的,出现了FLASH过小,无法烧录的情况。

2018-12-22 14:21

保存Block的位置信息。一旦固定了BRAM的位置,即可点击Vivado菜单栏内的保存按钮,这样就把BRAM的位置信息保存到了target约束

2019-01-29 14:14