数字设计中,“时钟”表示在寄存器间可靠地传输数据所需的参考时间。Vivado的时序引擎通过时钟特征来计算时序路径需求,通过计算裕量(Slack)的方法报告设计时序空余。时钟

2022-04-20 10:40

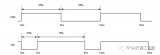

波形(waveform)以列表的形式给出,表中包含上升沿和下降沿在周期中的绝对时间,以ns为单位;第一个上升沿对应于第一个值,第一个下降沿对应第二个值;默认情况下,相位

2022-07-01 14:28

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado

2018-07-04 11:23

沿指令即在程序中用于检测信号的上升沿或下降沿的指令。

2023-07-20 14:20

在数字设计中,时钟代表从寄存器(register)到寄存器可靠传输数据的时间基准。

2024-01-04 09:16

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

2018-12-22 14:26

Xilinx Vivado开发环境编译HDL时,对时钟信号设置了编译规则,如果时钟由于硬件设计原因分配到了普通IO上,而非_SRCC或者_MRCC专用时钟管脚上时,编译

2024-04-15 11:38

在Vivado中新建IO Planning工程来初步引脚分配,这样会大大提高开发效率 在这里,你可以选择最右侧的开发板型号,也可以选择Part,具体的FPGA的型号,选择完后,我们可以很清晰的看到该型号的资源列表:包括IO数、可用的IO

2018-10-22 17:12

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到时钟向导IP,下面就介绍一下在vivad

2018-12-22 15:14

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado

2022-08-02 10:10