数字设计中,“时钟”表示在寄存器间可靠地传输数据所需的参考时间。Vivado的时序引擎通过时钟特征来计算时序路径需求,通过计算裕量(Slack)的方法报告设计时序空余。时钟

2022-04-20 10:40

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使

2017-11-30 09:14

其实这个分频时钟切换很简单,根本不需要额外的切换电路。一个共用的计数器,加一点控制逻辑,就可以了,而且可以实现2到16任意整数分频率之间的无缝切换。

2023-12-14 15:28

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado

2018-12-22 14:26

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到

2018-12-22 15:14

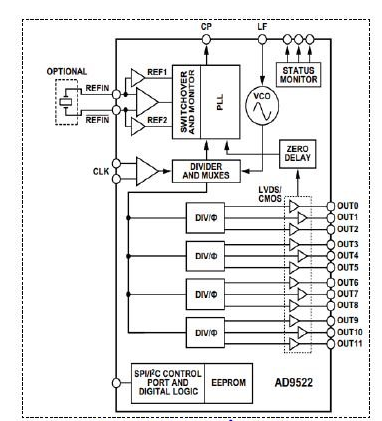

在集成度高度发展的今天,不能靠多个晶振源来解决问题,而且一旦晶振固定那么它的灵活性和可移植性必然受到很大影响,所以一些时钟分频芯片应运而生,今天我们将举一个很有代表性的AD9522时钟

2018-03-16 16:31

输入端分频因子(M)可从1~2047的分频范围内进行选择;输出端分频因子(N)可从1~4095的分频范围内进行选择。输出频率在1MHz~100MHz的范围内,输入

2018-08-15 11:16

生成时钟包括自动生成时钟(又称为自动衍生时钟)和用户生成时钟。自动生成时钟通常由PLL或MMCM生成,也可以由具有

2024-01-11 09:50

从分频方式看可以分为两种,一种是主动分频(PassiveCrossover),或者叫电子分频,也可以叫外置分频、有源分频

2019-10-08 10:37

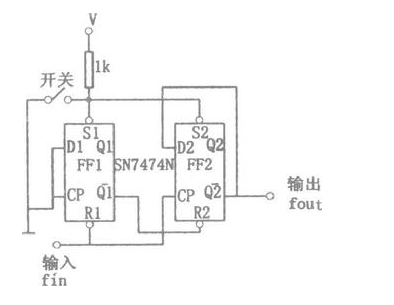

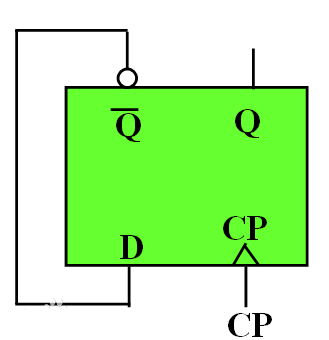

分频就是用同一个时钟信号通过一定的电路结构转变成不同频率的时钟信号。而二分频就是通过有分频作用的电路结构,在

2019-10-08 09:05