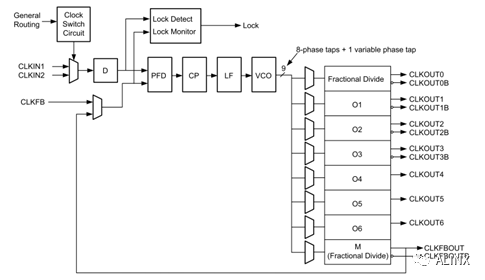

本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

2021-03-02 07:22

Vivado时钟的两大特性--时钟延迟和时钟的不确定性。

2017-11-17 11:38

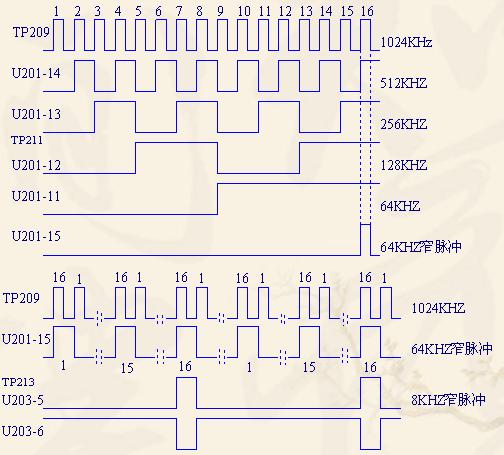

时钟使能电路是同步设计的基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但由于这些时钟是同源的,可以将它们转化为单一时钟处理;在ASIC中可以通过STA约束让分频

2023-01-05 14:00

时钟分频及定时变换电路

2009-10-11 10:35

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使

2017-11-30 09:14

数字设计中,“时钟”表示在寄存器间可靠地传输数据所需的参考时间。Vivado的时序引擎通过时钟特征来计算时序路径需求,通过计算裕量(Slack)的方法报告设计时序空余。时钟

2022-04-20 10:40

其实这个分频时钟切换很简单,根本不需要额外的切换电路。一个共用的计数器,加一点控制逻辑,就可以了,而且可以实现2到16任意整数分频率之间的无缝切换。

2023-12-14 15:28

单片机都是有时钟振荡器的。还有定时器,看门狗,程序计数器等等。如果看门狗或者定时器所要求的脉冲速度比较时钟脉冲慢,那么,就要利用分频器进行分频,以得到你所要求的脉冲速率

2017-11-15 10:07

,但是也有类似的功能模块,通过PLL可以倍频分频,产生其他很多时钟。本实验通过调用PLL IP core来学习PLL的使用、vivado的IP

2022-02-08 15:13

基于FPGA的高频时钟的分频和分频设计

2023-08-16 11:42