本文为大家介绍单端-差分转换器的电路详解。

2018-01-15 10:31

数字设计中,“时钟”表示在寄存器间可靠地传输数据所需的参考时间。Vivado的时序引擎通过时钟特征来计算时序路径需求,通过计算裕量(Slack)的方法报告设计时序空余。时钟

2022-04-20 10:40

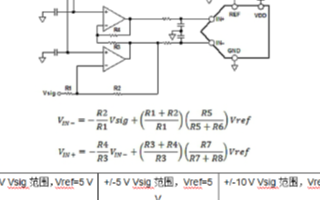

用这种方法实现的单端转差分具有最低的噪声,适合单电源类应用,可耐受阻性输入。 有关采用FDA的设计详情可参见应用笔记AN

2020-07-13 18:06

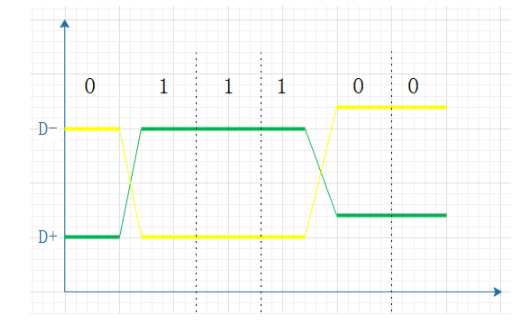

在射频领域,一般都是单端器件,走单端线;在数字硬件,走速率高的线,一般都是差分线。

2022-10-25 14:04

AD7982。该电路采用单端转差分驱动器ADA4941-1 和超低噪声5.0 V基准电压源ADR435 ,可以接受许多类型的单

2013-10-29 11:16

时钟域clock domain:以寄存器捕获的时钟来划分时钟域。单时钟域single clock domain,数据发送

2022-12-26 15:21

时钟域clock domain:以寄存器捕获的时钟来划分时钟域。 单时钟域single clock domain,数据

2022-08-29 15:11

CLKIN为外部输入时钟,如果是外部差分时钟信号,在MHS文件的PORT行指定*_p、*_n管脚均为同样的Net,如dcm_clk_s,差分极性分别指定正负即可。

2017-02-11 05:12

单端信号是相对于差分信号而言的,单端输入指信号有一个参考端和一个信号

2020-12-12 11:04