了解Vivado中的Logic Debug功能,如何将逻辑调试IP添加到设计中,以及如何使用Vivado Logic Analyzer与逻辑调试IP进行交互。

2018-11-30 06:22

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。本次带来Vivado系列,Vivado开发软件开发设计流程。话不多说,上货

2023-02-21 09:16

仿真功能概述 仿真FPGA开发中常用的功能,通过给设计注入激励和观察输出结果,验证设计的功能性。Vivado设计套件支持如下仿真工具:Vivado Simulator、Questa、ModelSim

2020-12-31 11:44

今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

2023-05-05 09:44

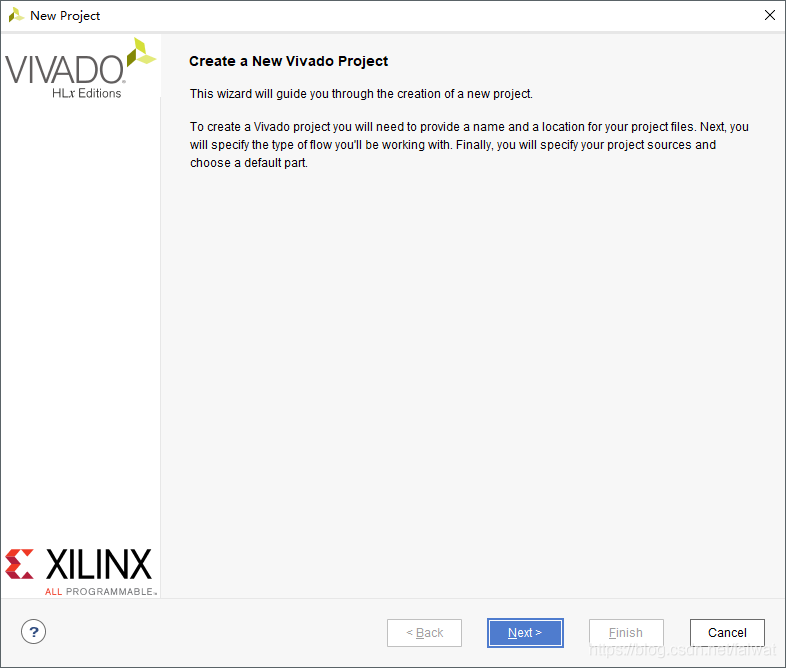

本文主要介绍如何使用Vivado 开发套件创建硬件工程。

2022-02-08 10:41

先给大家简单快速地介绍一下 Vivado 集成设计环境,即 IDE。当打开 Vivado 工程后,会有一个工程概要,向您介绍工程的设置、警告和错误信息以及工程的一般状态。

2012-04-25 09:00

在linux系统上实现vivado调用VCS仿真教程 作用:vivado调用VCS仿真可以加快工程的仿真和调试,提高效率。 前期准备:确认安装vivado软件和VCS软

2018-07-05 03:30

本文针对Vivado中实现的逻辑锁定和增量编译进行的工程实例介绍,文中有对应工程的下载地址。友情提示:(1)增量编译只允许修改当前工程不超过5%的时候才有效,一般应用于较大工程添加修改

2019-07-06 10:32

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑

2019-12-05 07:08

很久没有更新vivado+zedboard系列的博客了。前面的十篇博客主要介绍了Xilinx vivado工具的使用流程,vivado+zedboard裸机开发的方法以

2017-02-08 16:20