利用vivado进行设计xilinx FPGA时,写完设计代码和仿真代码后,点击run simulation(启动modelsim进行仿真)。

2025-08-30 14:22

为了尽快把新产品推向市场,数字系统的设计者需要考虑如何加速设计开发的周期。设计加速主要可以从“设计的重用”和“抽象层级的提升”这两个方面来考虑。Xilinx 推出的 Vivado HLS 工具可以

2025-04-16 10:43

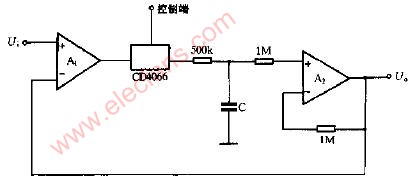

采样信号保持电路图

2009-05-08 14:28

版本迁移的操作想必大家已经做过不少了,其中包括从ISE转换到vivado与vivado老版本迁移到新版本。郑智海同学给大家介绍了一下如何把工程从ISE迁移到vivado中。

2023-01-30 09:11

在使用JTAG仿真器在vivado环境下抓信号时,报如下错误:

2023-11-14 10:37

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado

2018-07-04 11:23

本文使用 DDS 生成三个信号,并在 Vivado 中实现低通滤波器。低通滤波器将滤除相关信号。

2025-03-01 14:31

在Vivado中禁止自动生成BUFG(Buffered Clock Gate)可以通过以下步骤实现。 首先,让我们简要了解一下什么是BUFG。BUFG是一个时钟缓冲器,用于缓冲输入时钟信号,使其更稳

2024-01-05 14:31

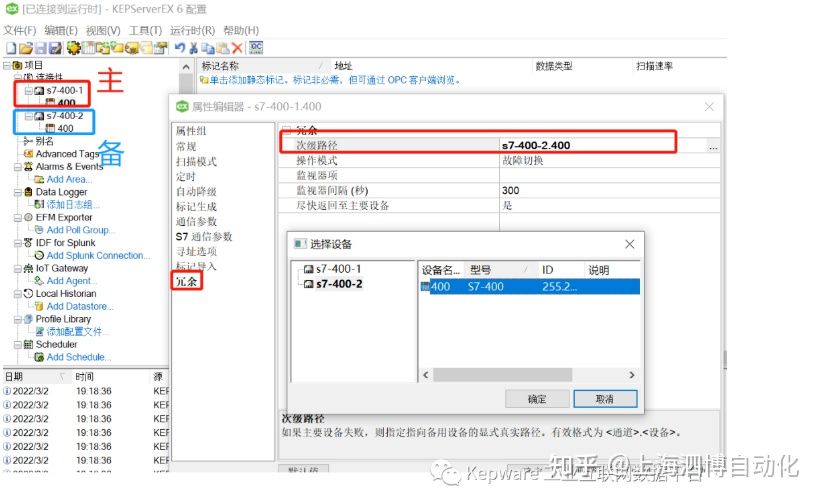

在工业通信领域中,为了确保系统的正常运行,减少故障时间,提高可靠性,通常都需要对系统进行冗余设置。在冗余配置的过程中经常会遇到一些这样那样的问题,下面就一起来看看,Kepware如何实现不同层级的冗余吧!Kepware针对工业现场通讯实现冗余主要分两个层级:设备层

2022-04-22 10:38

关键词:AD9100 , AD9618 , 跟踪-保持 , 信号采集 如图所示为具有跟踪-保持的中频(IF)信号采集电路。AD9100有着宽的动态范围,因此可以用于采集

2019-01-28 18:57