项目中主要用到的原语与IO端口有关,所以基本在Input/Output Functions 和IO两类中。下面着重介绍实际中所用到的几个原语,芯片A7系列。

2019-01-06 11:23

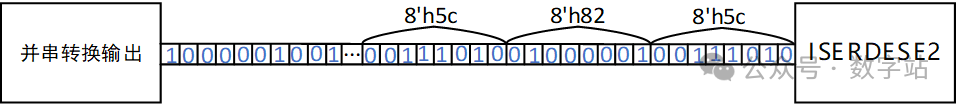

前面在讲解HDMI接口之前,讲解过IDDR、ODDR、OSERDESE2、IBUF等原语,之后一直有读者在问什么时候更新ISERDESE2这个原语。前文讲解过这些原语都在HDMI或者RGMII中使用过,但是ISERD

2025-03-17 10:52

在ISE中,可以很方便地生成RTL模块的实例化模板,Vivado其实也有这个功能,只是要通过Tcl命令实现,而且这个命令隐藏的比较深。以Vivado 2020.2为例,在菜单下选择Tools

2020-12-30 16:23

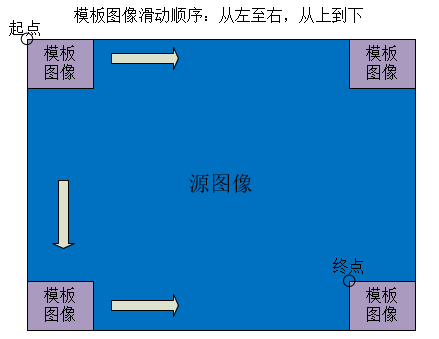

一:什么是模板匹配? 在OpenCV教程中这样解释模板匹配: 模板匹配是一项在一幅图像中寻找与另一幅模板图像最匹配(相似)部分的技术. 这里说的

2022-05-05 09:25

了解Vivado Design Suite 2016中的新功能。 我们将回顾新的UltraFast方法检查,HDL模块参考流程和用于IPI设计的SmartConnect IP,语言模板增强,Xilinx参数化宏(XPM),GUI改进

2018-11-20 06:22

UltraRAM 原语(也称为 URAM)可在 Xilinx UltraScale +™ 架构中使用,而且可用来高效地实现大容量深存储器。

2019-07-13 11:08

标准协议的规范中一般都对眼图模板都有详细的规定,使用 IBERT 完成眼图扫描后,通过设置一些参数,即可让 Vivado 自动将模板画到眼图上,具体操作步骤如下。

2023-06-28 10:42

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado

2018-07-04 11:23

最近,需要使用VCS仿真一个高速并串转换的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原语。而此前我只使用VCS仿真过Quartus的IP核。

2023-06-06 11:09

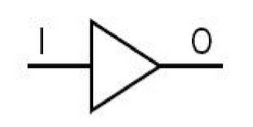

Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。下面分别对其进行详细介绍。

2022-02-08 14:01