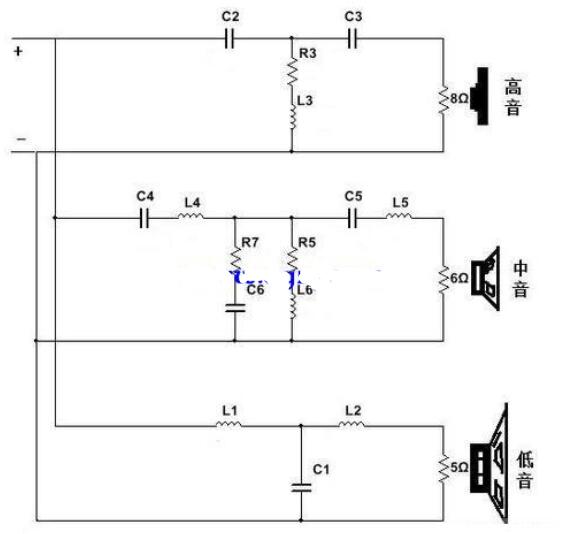

两路两分频系统的中低音/高音的分频点的选择,除了要遵循关于中低音,高音的特性选择外,一般地,在汽车音响中由于两分频系统的单元距离较远,分频点宜低不宜高,这可以尽量避免中

2019-10-09 09:29

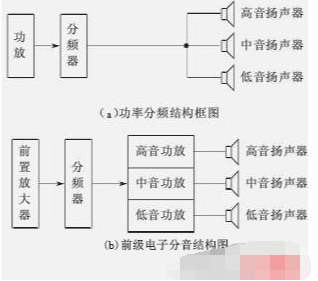

音响中分频器和功放有两种连接方式。一种是电子分频器(有源分频),既前级出来后进入分频器,然后单声道分双路或者三路分别送往各功放输出给音箱,对于立体声而言,单声道功放最少

2021-05-01 17:55

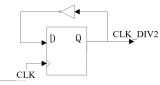

通常情况下,时钟的分频在FPGA设计中占有重要的地位,在此就简单列出分频电路设计的思考思路。

2020-07-10 17:18

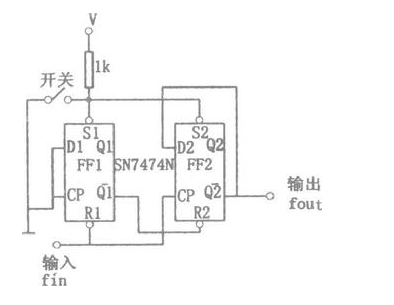

使用计数器来做分频,首先计数。例如采用16计数器。每来一次外部时钟,记一次数,当计数到16时,计数器输出一个方波。然后重新计数。当再次达到16时再次输出,这样就形成了16分频。

2019-10-08 10:44

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

2018-12-22 14:26

从分频方式看可以分为两种,一种是主动分频(PassiveCrossover),或者叫电子分频,也可以叫外置分频、有源分频

2019-10-08 10:37

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到时钟向导IP,下面就介绍一下在vivado中进行PL开发时调用IP的方法。

2018-12-22 15:14

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado

2018-07-04 11:23

初学 Verilog 时许多模块都是通过计数与分频完成设计,例如 PWM 脉宽调制、频率计等。而分频逻辑往往通过计数逻辑完成。本节主要对偶数分频、奇数分频、半整数

2023-03-29 11:38

缺点:当分频倍数很大时,需要的寄存器也是倍增。当然你也可以采用复用的方式去减少所需寄存器数目,例如,36分频,可以做两个6分频器相连,则所需寄存器为6个,需要的寄存器数大大减少。

2018-12-08 10:40