在做模块划分时,通常会出现这种情形,某个大的模块中包含了一个或多个功能子模块,verilog是通过模块调用或称为

2025-05-03 10:29

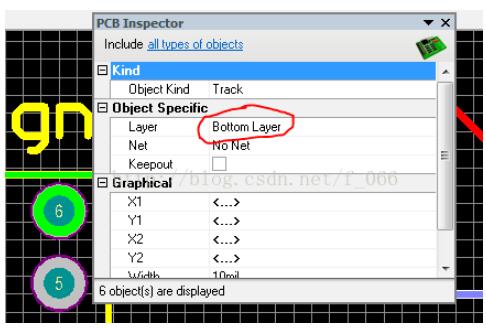

本文主要详细介绍了pcb顶层和底层互换,把PCB切换到顶层,然后Edit/select/allonlayer选择顶层。

2019-04-26 15:47

顶层金属工艺是指形成最后一层金属互连线,顶层金属互连线的目的是实现把第二层金属连接起来。顶层金属需要作为电源走线,连接很长的距离,需要比较低的电阻,需要很大的宽度以支持很大的电流。

2024-10-29 14:09

Verilog模块之间的连接是通过模块端口进行的。 为了给组成设计的各个模块定义端口,我们必须对期望的硬件设计有一个详细的认识。 不幸的是,在设计的早期,我们很难把握设

2023-06-12 10:05

本文首先介绍了verilog的概念和发展历史,其次介绍了verilog的特征与Verilog的逻辑门级描述,最后介绍了Verilog晶体管级描述与

2018-05-14 14:22

顶层金属 AI工艺是指形成顶层金属 AI 互连线。因为 Cu很容易在空气中氧化,形成疏松的氧化铜,而且不会形成保护层防止铜进一步氧化,另外,Cu 是软金属,不能作绑定的金属,所以必须利用AL 金属

2024-11-25 15:50

Verilog设计的仿真需求。 编写测试文件 : 编写Verilog测试文件,对设计的各个模块进行测试。测试文件应覆盖各种情况,包括正

2024-12-17 09:50

模块是Verilog 的基本描述单位,用于描述某个设计的功能或结构及其与其他模块通信的外部端口。

2017-02-11 16:58

体声明、信号声明、顶层设计实例化、提供激励;Verilog的仿真文件应包括:模块声明、信号声明、顶层设计实例化、提供激励。大致思想都是相似的。

2023-09-09 10:16

使用Verilog描述硬件的基本设计单元是模块(module)。构建复杂的电子电路,主要是通过模块的相互连接调用来实现的。模块被包含在关键字module、endmodu

2017-12-08 17:20