“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括Verilog仿真时常用的系统任务、双向端口的使用(inout)、边沿检测”

2022-03-15 13:34

使用Verilog进行数字电路设计是一个复杂但有序的过程,它涉及从概念设计到实现、验证和优化的多个阶段。以下是一个基本的步骤指南,帮助你理解如何使用Verilog来设计数字

2024-12-17 09:47

HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

2022-08-31 09:06

本文首先介绍了verilog的概念和发展历史,其次介绍了verilog的特征与Verilog的逻辑门级描述,最后介绍了Verilog晶体管级描述与

2018-05-14 14:22

Circuit,专用集成电路)设计是一个复杂的过程,涉及到逻辑设计、综合、布局布线、物理验证等多个环节。在这个过程中,Verilog被用来描述数字电路的行为和结构,进而实现ASIC的设计。 具体来说

2024-12-17 09:52

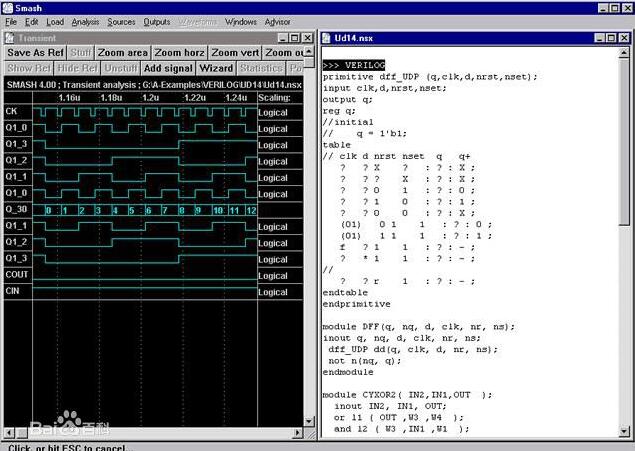

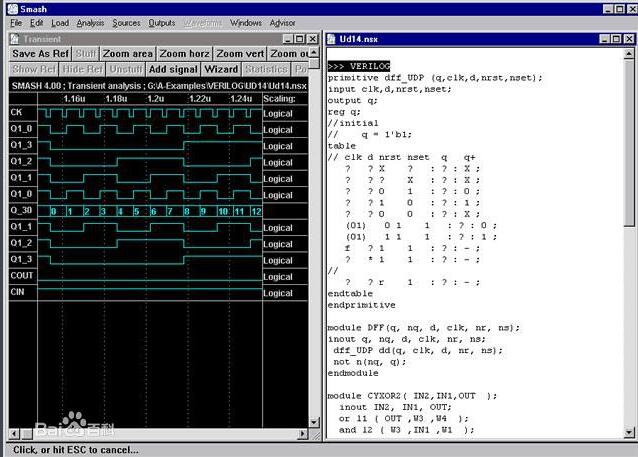

Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统对

2017-02-11 16:57

IEEE标准。 这两种语言都是用于bai数字电子系统设计的硬件描述语言,而且都已经zhi是 IEEE 的标准。 VHDL 1987 年成为dao标准,而 Verilog 是 1995 年才成为标准

2020-06-17 16:13

Verilog提供了很多对文件操作的系统任务和函数,例如打开关闭文件、向文件写入值、从文件读出值等等。

2022-12-05 13:57

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示

2018-03-23 11:46

国国防部确认为标准硬件描述语言 。Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图

2018-03-23 16:43