使用Verilog描述硬件的基本设计单元是模块(module)。构建复杂的电子电路,主要是通过模块的相互连接调用来实现的。模块被包含在关键字module、endmodule之内。实际的电路元件。Verilog中的模块

2017-12-08 17:20

Verilog 是一种硬件描述语言 (HDL),主要用于描述数字电子电路的行为和结构。在 Verilog 中,函数 (Function) 是一种用于执行特定任务并返回一个值的可重用代码块。

2024-02-22 15:49

在verilog中,函数和任务均用来描述共同的代码段,并且在模式内任意位置被调用,提高代码效率,让代码更加的直观,提高代码可读性。但是在实际使用的过程中,函数和任务也存在诸多的不同,下面将对而这进行

2024-02-12 18:43

其中,返回值的类型和位宽是可选项,如果缺省会返回一位寄存器类型数据。Verilog HDL认为函数的定义隐式地声明了与函数同名的寄存器。函数的定义把

2021-07-02 10:24

任务和函数在Verilog中用于描述常用的功能行为。与其在不同的地方复制相同的代码,不如根据需求使用函数或任务,这是一种良好且常见的做法。为了便于代码维护,最好使用子例程之类的

2022-03-15 11:01

小技巧分享: verilog下取对数其实可用$clog2这个系统函数,和自己找代码里面写入function是同样的效果,但是方便的多。这是verilog 2005就开始支持的标准,所以vivado

2021-10-09 15:29

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括Verilog仿真时常用的系统任务、双向端口的使用(inout)、边沿检测”

2022-03-15 13:34

在做模块划分时,通常会出现这种情形,某个大的模块中包含了一个或多个功能子模块,verilog是通过模块调用或称为模块实例化的方式来实现这些子模块与高层模块的连接的.

2025-05-03 10:29

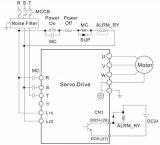

plc控制伺服,如何实现暂停功能,基本可以从硬件和软件的方面去实现伺服电机的暂停功能。硬件方面就是断开伺服驱动器的电源,在这里一般都有一个常闭的信号接到驱动器电源的接触

2019-07-02 15:43

在 Verilog 中,可以利用任务(关键字为 task)或函数(关键字为 function),将重复性的行为级设计进行提取,并在多个地方调用,来避免重复代码的多次编写,使代码更加的简洁、易懂。

2023-06-01 16:31