本文首先介绍了verilog的概念和发展历史,其次介绍了verilog的特征与Verilog的逻辑门级描述,最后介绍了Verilog晶体管级描述与

2018-05-14 14:22

Verilog测试平台设计方法是Verilog FPGA开发中的重要环节,它用于验证Verilog设计的正确性和性能。以下是一个详细的Verilog测试平台设计方法及

2024-12-17 09:50

宏定义尤其是带参数的宏定义,特别容易出现一些隐藏问题,因为宏定义在预处理阶段是按照定义原封不动的进行展开,此时如果展开之后涉及到运算符优先级的问题,那么隐藏bug就此出

2023-10-20 15:26

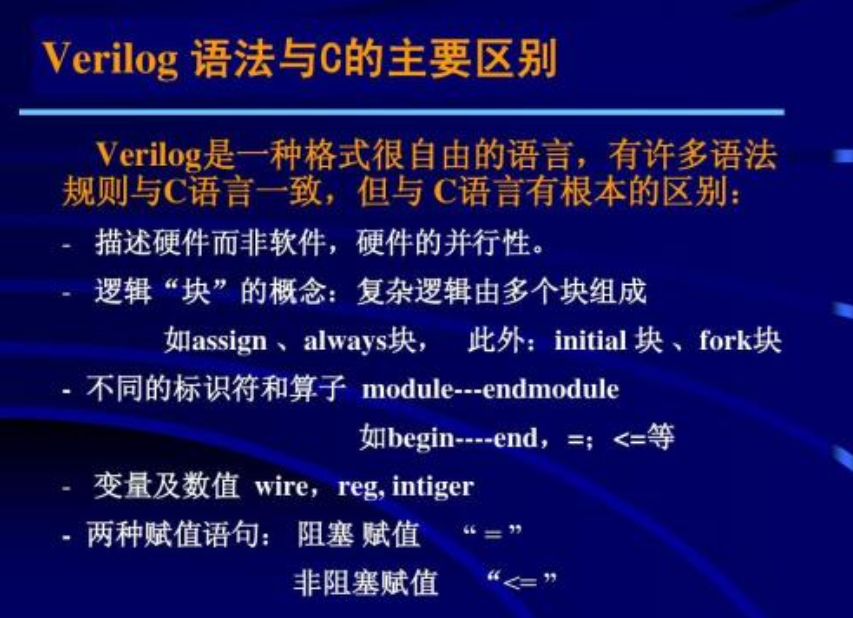

Verilog 与 VHDL 比较 1. 语法和风格 Verilog :Verilog 的语法更接近于 C 语言,对于有 C 语言背景的工程师来说,学习曲线较平缓。它支持结构化编程,代码更直观,易于

2024-12-17 09:44

Verilog与ASIC设计的关系 Verilog作为一种硬件描述语言(HDL),在ASIC设计中扮演着至关重要的角色。ASIC(Application Specific Integrated

2024-12-17 09:52

这一点和函数是不同的:在函数中,形参和实参是两个不同的变量,都有自己的作用域,调用时要把实参的值传递给形参;而在带参数的宏中,只是符号的替换,不存在值传递的问题。

2017-12-02 10:19

介绍几种自动生成verilog代码的方法。

2024-11-05 11:45

Verilog模块之间的连接是通过模块端口进行的。 为了给组成设计的各个模块定义端口,我们必须对期望的硬件设计有一个详细的认识。 不幸的是,在设计的早期,我们很难把握设计的细节。 而且,一旦模块

2023-06-12 10:05

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括Verilog仿真时常用的系统任务、双向端口的使用(inout)、边沿检测”

2022-03-15 13:34

学习verilog最重要的不是语法,“因为10%的语法就能完成90%的工作”,verilog语言常用语言就是always@(),if~else,case,assign这几个了。

2018-03-26 14:06