Icarus Verilog(以下简称iverilog )号称“全球第四大”数字芯片仿真器,也是一个完全开源的仿真器。

2022-08-15 09:11

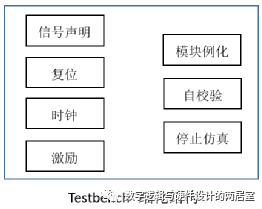

Verilog 代码设计完成后,还需要进行重要的步骤,即逻辑功能仿真。仿真激励文件称之为 testbench,放在各设计模块的顶层,以便对模块进行系统性的例化调用进行仿真

2023-06-02 11:35

本文将介绍如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真。 Icarus Verilog Icarus

2021-07-27 09:16

采用System Verilog语言设计了一种具有层次化结构的可重用验证平台,该平台能够产生各种随机、定向、错误测试向量,并提供功能覆盖率计算。将验证平台在Synopsys公司的VCS仿真工具上运行

2018-01-12 11:28

基于Verilog的顺序状态逻辑FSM的设计与仿真 硬件描述语言Verilog为数字系统设计人员提供了一种在广泛抽象层次上描述数字系统的方式,同时,为计算机辅助设计工具

2010-02-04 09:32

。然而,在实际应用中,设计师可能会遇到各种问题,这些问题可能会影响仿真的准确性和设计的可靠性。 Verilog电路仿真常见问题 仿真环境的搭建问题

2024-12-17 09:53

引起的差异,就可能产生错误的激励,无法保证仿真结果的正确,本文就是区分各种延时赋值语句的差异,并给出比较结果。 1:阻塞式左延时赋值语句 举例说明如下: module adder_t1 (co, sum

2020-11-25 15:29

只作为语法设定来介绍,忽略了Verilog语言的软件特性和仿真特性。使得初学者无法理解Verilog语言在行为级语法(过程块、赋值和延迟)背后隐藏的设计思想。本文尝试从仿真

2023-05-25 15:10

Verilog语言是一种硬件描述语言(HDL),用于描述数字逻辑电路和系统。它是一种非常强大且广泛使用的语言,在数字电路设计中扮演着重要的角色。其中, inout 是Verilog中的一种信号类型

2024-02-23 10:15

我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。 源文件内容如下:

2023-05-11 17:03