不做讲解。如图所示电压传感器可监测芯片的VCCINT,VCCAUX,VCCBRAM等,PL_SYSMON的VP_0和VN_0为一对专用的ADC模拟输入口。VAUXP[*]和VAUXN[*]也是ADC输入口,但是不用作ADC输入口时,可用作普通IO使用。本实验主要测

2021-01-29 10:03

监测芯片的VCCINT,VCCAUX,VCCBRAM等,VP_0和VN_0为一对专用的ADC模拟输入口。VAUXP[*]和VAUXN[*]也是ADC输入口,但是不用作ADC输入口时,可用作普通IO使用。

2022-04-12 19:37

的VCCINT,VCCAUX,VCCBRAM等,VP_0和VN_0为一对专用的ADC模拟输入口。VAUXP[*]和VAUXN[*]也是ADC输入口,但是不用作ADC输入口时,可用作普通IO

2021-05-27 11:30

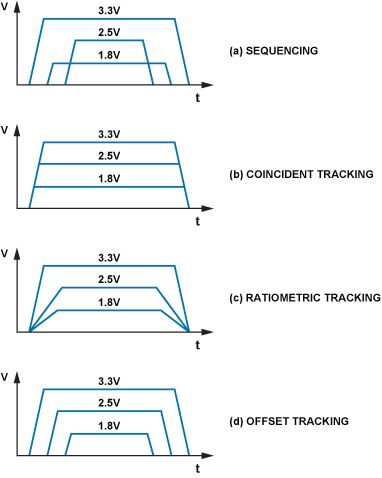

电源应选择输出电流大于器件最大要求电流的DCDC供电,原则上DCDC的开关频率越高需要的功率电感和滤波电容体积就越小,根据板级实际情况选择开关频率。

2022-11-01 14:21

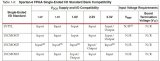

SelectIO Resources》后,得到了以下信息:Spartan-6的供电来源于3个引脚:VCCINT、VCCO、VCCAUX。 VCCINT is the main power supply for th

2017-02-08 10:36

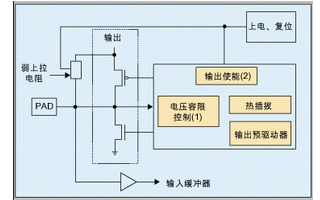

PLD热插拔的基本原理是在加电(VCCINT或任何VCCIO电源)或关电过程中关断输出缓冲。当VCCINT或VCCIO低于阈值电压时,热插拔电路都会产生一个内部的HOTSCKT信号,HOTSCKT信号将关断输出缓冲,以便确保没有直流电流通过管脚(不包括通过弱上拉电

2020-09-02 12:06

泄漏方面做了许多努力,尽管如此,源于泄漏的静态功耗在最差和典型工艺条件下的变化仍然有2:1。泄漏功耗受内核电压(VCCINT)的影响很大,大约与其立方成比例,哪怕VCCINT仅上升5%,静态功耗就会提高约 15%。最后,泄漏电流还与结(或芯片)温密切相关。

2020-07-21 17:56

为V首席运营官, V科考和 VCCINT.这些电源分别用于为 FPGA 内核、辅助电路(如时钟和 PLL)和接口逻辑供电。

2023-01-29 10:44

MAX15303降压型开关稳压器提供3A输出电流能力。VCCINT输出设置为0.72V,利用MAX20730 PMBus™降压型开关稳压器提供12A输出电流能力。

2023-06-12 14:50

VCCINT:核心工作电压,PCI Express (PCIe) 硬核IP 模块和收发器物理编码子层(PCS) 电源。一般电压都很低,目前常用的FPGA都在1.2V左右。为FPGA的内部各种逻辑供电

2019-02-27 14:09