问题:在HW-USB-FLYLEADS-G电缆上使用的最大布线长度是多少?请看下面的图片。背景:我使用HW-USB-FLYLEADS-G电缆和DLC10平台电缆USB

2020-05-20 07:45

所谓相对的就是要求走线长度保持一致,保证信号同步到达若干个接收器。有时候在PCB上的一组信号线之间存在着相关性,比如总线,就需要对其长度进行校正,因为需要信号在接收端同步。其调整方法就是找出其中长的那根走线,然后将其

2023-09-01 17:33

大家好,我正在研究我的第一个Kintex7 DDR3接口。为了实现RAM,我想在PCB上包含长度匹配的封装走线长度。要获取包延迟信息,我使用了命令(在Vivado中)link_design

2020-08-12 10:17

数字系统对时序要求严格,为了满足信号时序的要求,对PCB上的信号走线长度进行调整已经成为PCB设计工作的一部分。调整走线长度包括两个方面:相对的和绝对的。 所谓相

2018-11-27 15:22

高速数字电路互连时序模型与布线长度分析 高速电路设计领域,关于布线有一种几乎是公理的认识,即等长走线,认为走线只要等长就一定满足时序需求,就不会存在时序问题。本文对常用高速器件的互连时序建立模型,并

2017-10-15 10:24

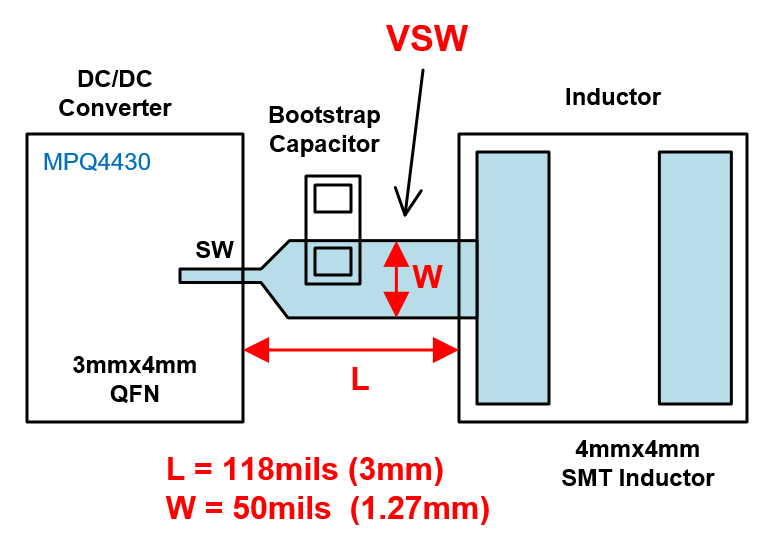

PCB布局的关键:尽量缩短开关节点走线长度?|深圳比创达EMC(2)

2023-08-07 11:20

为了保证良好的信号质量, USB 2.0 端口数据信号线按照差分线方式走线。为了达到USB 2.0 高速 480MHz 的速度要求,建议 PCB 布线设计采用以下原则:

2019-05-23 08:52

如果您阅读了许多PCB设计指南,尤其是有关并行协议和差分对布线的指南,则将看到很多关于走线长度匹配的内容。当您需要进行迹线长度匹配时,您的目标是最大程度地减少串行协议中

2021-01-05 10:56

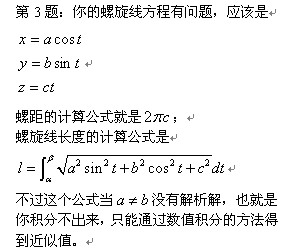

螺旋线长度计算公式

2007-12-11 13:56

经常看到有文章介绍对SDRAM布线的各种要求,这只是工程上的经验总结,不同的芯片对时序的要求不同,对走线也有不同的要求,不能一概而论。其实,等长不是目的,真正的目的是满

2011-11-16 12:49