由于 PCB 板的密度越来越高,许多 PCB LAYOUT 工程师在走线的过程中,较容易出现一种失误,即时钟信号等高速信号网络,在多层的

2024-01-08 15:33

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高

2019-07-01 15:24

本文主要详解PCB设计高速模拟输入信号走线,首先介绍了PCB设计高速模拟输入信号走

2018-05-25 09:06

规则一:高速信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信号线

2017-11-25 07:43

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建

2019-03-15 14:05

在高速的 PCB 设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成 EMI 的

2024-01-10 16:03

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

2019-12-16 14:52

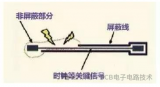

规则一:高速信号走线屏蔽规则 如上图所示: 在高速的PCB设计中,时钟等关键的高速信号

2020-02-14 11:53

如何避免高速PCB设计中传输线效应 1、抑止电磁干扰的方法 很好地解决信号完整性问题将改善PCB板的电磁兼容性(EMC)。其中非常重要的是保证

2009-11-20 11:17

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号

2023-05-22 09:15