这篇文章在开发者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 传统 IDE) 的基础上撰写,但使用的是 AMD Vitis Unified IDE,而不是之前传统版本的 Vitis HLS。

2025-06-20 10:06

您将在这篇博客中了解系统设备树 (SDT) 以及如何在 AMD Vitis Unified IDE 中使用 SDT 维护来自 XSA 的硬件元数据。本文还讲述了如何对 SDT 进行操作,以便在 Vitis Unified IDE 中实现更灵活的使用场景。

2025-11-18 11:13

Vivado IP 流程(Vitis Unified),在这篇 AMD Vitis HLS 系列 3 中,我们将介绍如何使用 Unified IDE 创建 HLS 组件。这里采用“自下而上”的流程,从 HLS

2025-07-02 10:55

在本篇文章我们将学习如何在 AMD Vitis Unified 2024.2 中连接到 QEMU。 这是本系列的第 2 篇博文。要了解如何设置和使用 QEMU + 协同仿真,请参阅开发者分享|在 AMD Versal 自适应 SoC 上使用简单的 QEMU + 协同仿真示例。

2025-08-06 17:24

许久没更新了,间歇性来写写,还是继续Modelsim中关于内存的操作,涉及的文件可在文末自行获取,本篇对应memory的文件夹。

2022-10-24 10:16

Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

2023-11-14 17:49

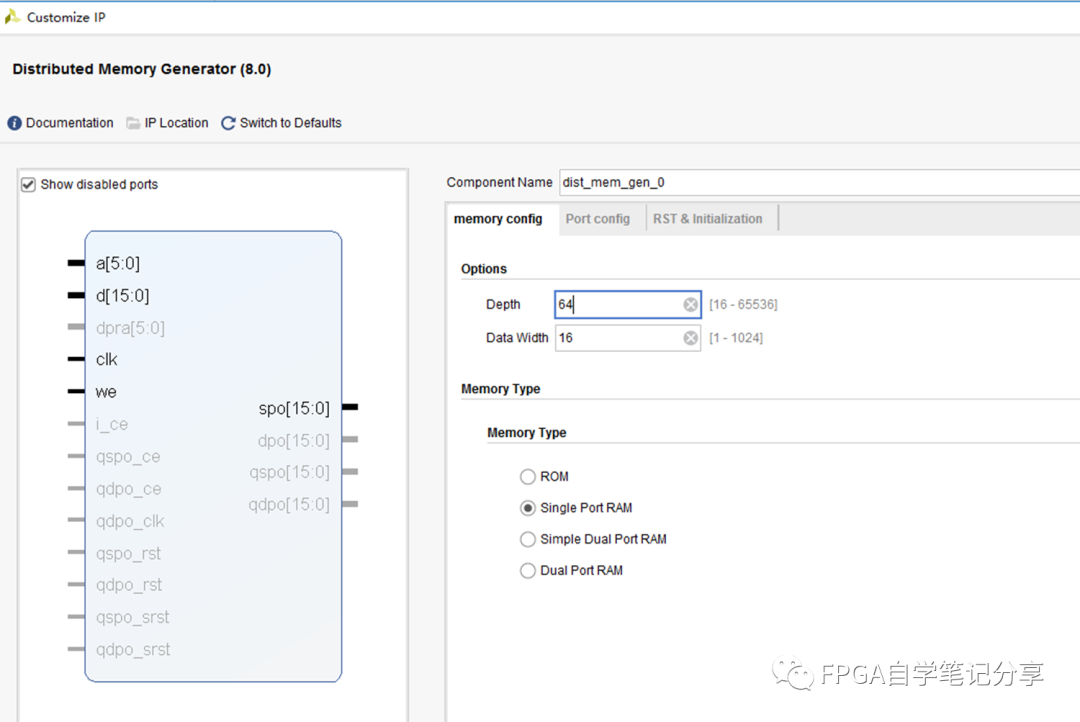

Distributed Memory Generator IP 核采用 LUT RAM 资源创建各种不同的存储器结构。IP可用来创建只读存储器 (ROM)、单端口随机存取存储器 (RAM) 和简单双

2023-11-17 17:00

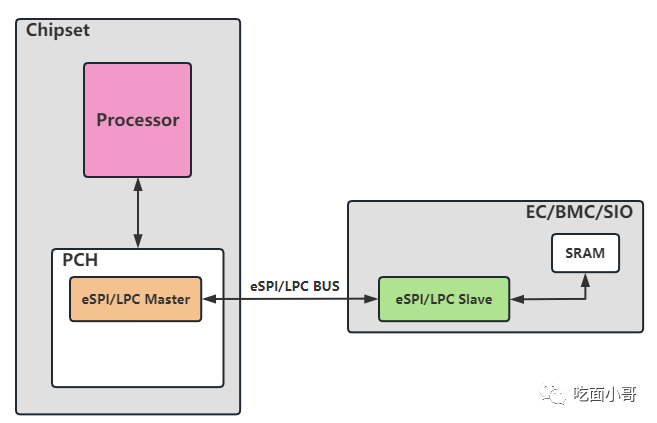

ShareMemory,顾名思义就是共享内存。这个概念在很多计算机系统中都存在,本文特指 EC SRAM 映射到 CPU Memory 空间的共享内存设计。

2023-11-18 15:11

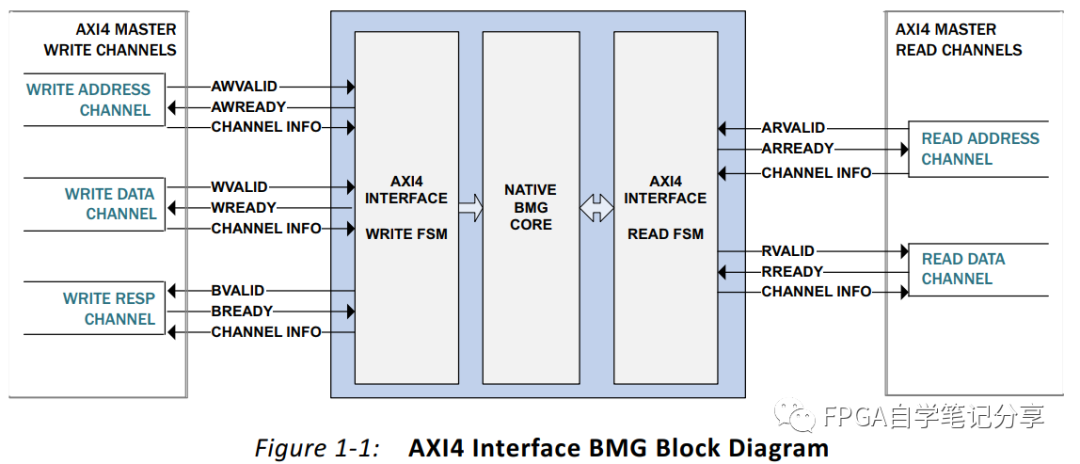

之前的文章对Block Memory Generator的原生接口做了说明和仿真,本文对AXI接口进行说明。

2023-11-14 18:25

shadow memory检测原理的实现主要就是__asan_load##size()和__asan_store##size()函数的实现。那么KASAN是如何根据访问的address以及对应的shadow memory的状态值来判断访问是否合法呢?首先看一种最简

2018-09-03 15:00