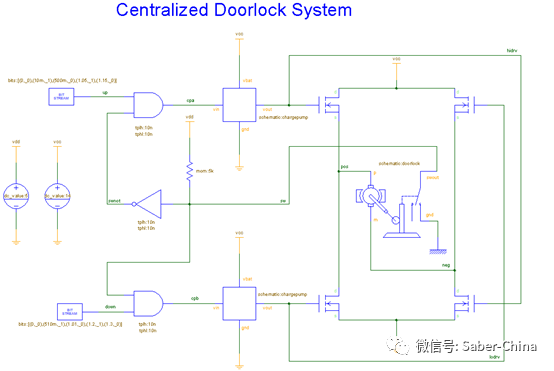

Saber是Synopsys公司的模拟及混合信号仿真软件,可以同时对模拟信号、事件驱动模拟信号、数字信号以及模数混合信号设备进行仿真。

2023-12-05 10:16

SPICE模型发展至今,己经在电子设计业中得到了广泛的应用,并且还派生出许多不同的版本,其中最为主要的两个是HSPICE和PSPICE.其中由Avant公司(现己被Synopsys公司兼并)开发的HSPICE运行于工

2019-10-12 14:39

本文对HDTV芯片,从编码和综合两个方向入手,提出了解决方案。通过使用Synopsys公司的综合器Design Compiler,采用Top-down的方法对设计进行综合。结果表明综合方案较好的满足了综合目标,效果

2011-08-28 17:31

下一步, 就是要把这些东西变成实实在在的电路:小Boss.综合电路:推荐武器: Design Compiler (DC)数字电路需要用到Design Compiler, Synopsys公司出的大杀

2019-05-05 14:46

在特定条件下采用更智能的技术来隔离特定错误,找到问题电路的源头并渐进式修复错误,这很重要。Synopsys 公司的Synplify Premier 和Synplify Pro FPGA设计工具以及Identify RTLDebugger 等产品能帮助设计人员完成上

2013-08-15 09:59

采用System Verilog语言设计了一种具有层次化结构的可重用验证平台,该平台能够产生各种随机、定向、错误测试向量,并提供功能覆盖率计算。将验证平台在Synopsys公司的VCS仿真工具上运行

2018-01-12 11:28

saber仿真软件是美国Synopsys公司的一款EDA软件,被誉为全球最先进的系统仿真软件,是唯一的多技术、多领域的系统仿真产品,现已成为混合信号、混合技术设计和验证工具的业界标准,可用于电子

2017-12-08 11:18

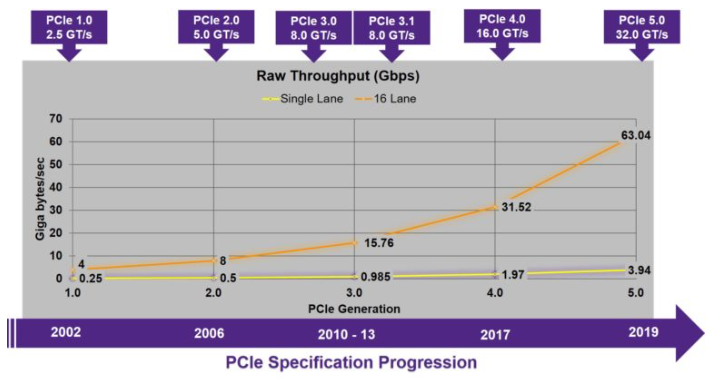

PCI Express® 5.0规范,达到32GT / s的传输速率,同时保持低功耗和与前几代技术的向后兼容性。为此,Synopsys 还宣布与 Astera Labs 合作开发业界首款 PCIe

2023-05-26 10:41

VCLP(VC Low Power)是Synopsys提供的一款低功耗静态规则检查工具,它能够帮助验证和清洁IEEE 1801 Unified Power Format (UPF)低功耗设计意图,并确保UPF中的功耗意图与实现一致。

2024-04-15 11:25

和静态时序分析工具一起来完成对电路完备的验证。本文就以Synopsys公司的formality工具为例,来介绍形式验证的流程和基本概念,后续会详细介绍使用formality做RTL2Gate流程中每一步骤的操作。

2022-12-27 15:18