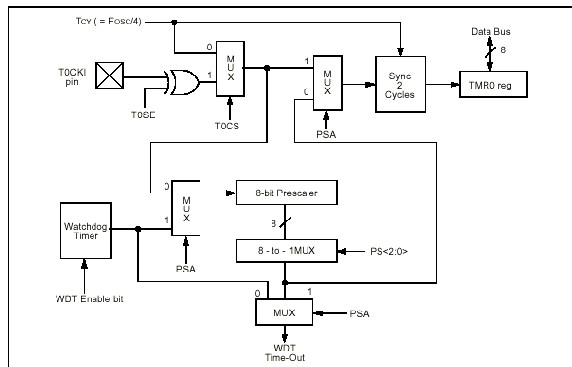

1、从RTCC到WDT的改变 MOVLW B‘XX0X0XXX’ ;选择内部时钟和新的预分频值 OPTION ;如果新的预分频值=“000”或者 CLRF RTCC ;=“001”,则

2018-11-08 16:14

预分频是为了得到不同频率值所设定的寄存器相当于系数比如说晶振是30M的预分频为2那么得到的就是 30/2=15M与倍频是相反的功能 当然还有后分频道理是一样的。

2017-11-15 17:42

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1

2017-11-30 09:14

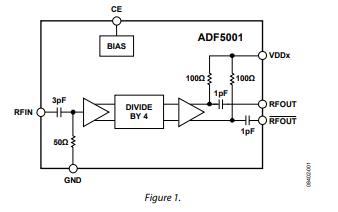

ADI 公司推出低功耗射频预分频器-- ADF500x 射频预分频器电路工作频率可达 18GHz,功耗非常低,可与业界领先的 ADI PLL 合成器配套使用 &nbs

2010-05-11 16:27

关于USART波特率、TIM的外设预分频值

2020-03-06 14:52

如输出到称为HCLK、FCLK的时钟,还直接输出到SDIO外设的SDIOCLK时钟、存储器控制器FSMC的FSMCCLK时钟,和作为APB1、APB2的预分频器的输入端

2018-04-03 08:45

家庭影院套装的分频数 我们知道,人可以听到的声音的频率范围是在20Hz—20kHz之间,祈望仅使用一只

2010-01-04 15:54

标出;图中间的时钟监视系统(CSS)是在很多ST7的单片机中就出现的安全设置。 特别注意 :图的右边,输出定时器时钟之前有一个乘法器,它的操作不是由程序控制的,是由硬件根据前一级的APB预分频器的输出自动选择,当AP

2017-12-04 17:00

时钟使能电路是同步设计的基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但由于这些时钟是同源的,可以将它们转化为单一时钟处理;在ASIC中可以通过STA约束让分频

2023-01-05 14:00

ADF5001预分频器是一款低噪声、低功耗、固定RF分频器模块 ,可用来将高达18GHz的频率分频至适合输入到[ADF4156]或 [ADF4106]等PLL IC的较低频率。ADF5001提供4

2025-04-16 15:50