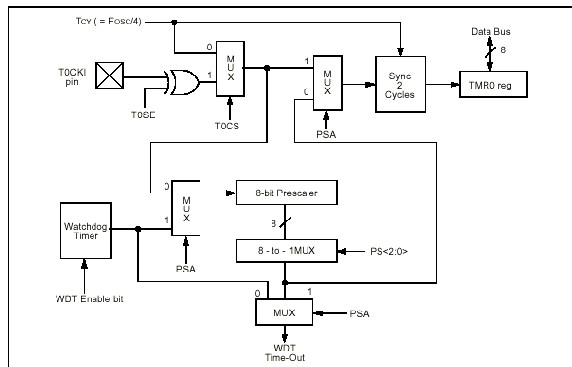

1、从RTCC到WDT的改变 MOVLW B‘XX0X0XXX’ ;选择内部时钟和新的预分频值 OPTION ;如果新的预分频值=“000”或者 CLRF RTCC ;=“001”,则

2018-11-08 16:14

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1

2017-11-30 09:14

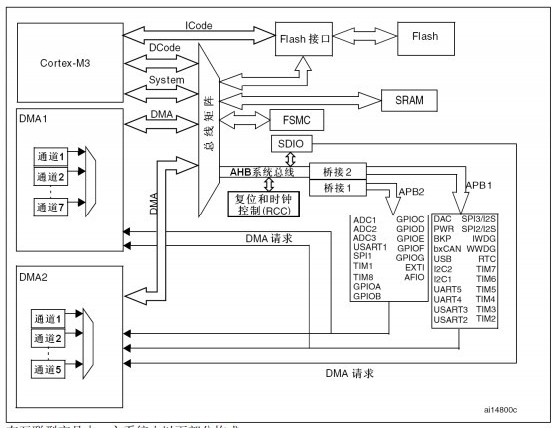

如输出到称为HCLK、FCLK的时钟,还直接输出到SDIO外设的SDIOCLK时钟、存储器控制器FSMC的FSMCCLK时钟,和作为APB1、APB2的预分频器的输入端

2018-04-03 08:45

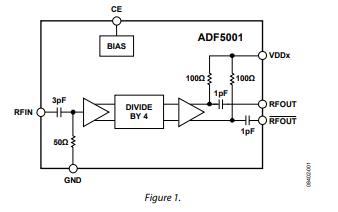

ADF5001预分频器是一款低噪声、低功耗、固定RF分频器模块 ,可用来将高达18GHz的频率分频至适合输入到[ADF4156]或 [ADF4106]等PLL IC的较低频率。ADF5001提供4

2025-04-16 15:50

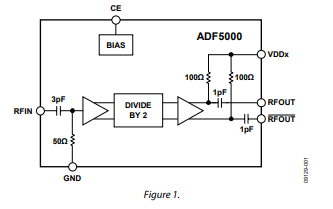

ADF5000预分频器是一款低噪声、低功耗、固定RF分频器模块,可用来将高达18 GHz的频率分频至适合输入到[ADF4156]等PLL IC的较低频率。ADF5000提供2分

2025-04-16 15:16

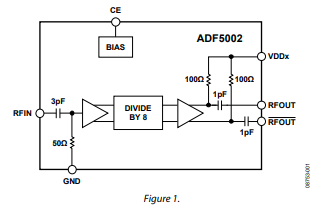

ADF5002预分频器是一款低噪声、低功耗、固定RF分频器模块,可用来将高达18GHz的频率分频至适合输入到 [ADF4156]或[ADF4106]等PLL IC的较低频率。ADF5002提供8

2025-04-16 15:46

其实这个分频时钟切换很简单,根本不需要额外的切换电路。一个共用的计数器,加一点控制逻辑,就可以了,而且可以实现2到16任意整数分频率之间的无缝切换。

2023-12-14 15:28

和PWM)等。 使用定时器预分频器和RCC时钟控制器预分频器,脉冲长度和波形周期可以在几个微秒到几个毫秒间调整。STM32

2018-10-30 16:10

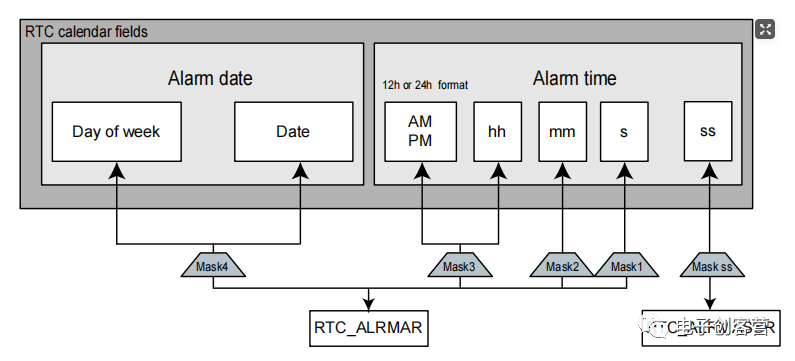

通过两个预分频得到1hz的时钟用来更新日历。

2023-10-24 14:30

用户可通过多个预分频器配置AHB总线、高速APB2总线和低速APB1总线的频率。AHB和APB2域的最大频率是72MHZ。APB1域的最大允许频率是36MHZ。SDIO接口的时钟频率固定为HCLK/2。

2017-11-30 09:01