指上电时候的reset,通过复位按键来对整个chip进行reset。该reset是全局的,所有的模块内部寄存器都会被reset掉,该

2018-04-20 17:33

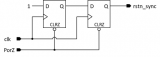

复位同步电路 reset synchronizer 其实只在复位信号 release 的时候派上用场。复位结束后,这个电路其实就没用了。 但这个电路的时钟还在 switch,这个电路还在耗电。

2024-02-19 09:21

嵌入式系统 的应用领域越来越广泛,干扰或者恶劣环境常影响嵌入式系统运行的 稳定性 和可靠性。 Reset 是维护系统稳定的一个关键因素,正确地设计复位电路,巧妙地应用复位操作,能使整个系统更可靠、稳定地运行。本文结合实际项目经验分析Reset的相关应用与设计,展示

2018-02-07 09:04

现在的FPGA算法的实现有下面几种方法: 1. Verilog/VHDL 语言的开发 ; 2. system Generator; 3. ImpulsC 编译器实现从 C代码到 HDL 语言; 4.

2017-11-17 14:29

system generator是xilinx公司的系统级建模工具,它是扩展mathworks公司的MATLAB下面的simulink平台,添加了XILINX FPGA专用的一些模块。加速简化了FPGA的DSP系统级硬件设计。

2017-02-11 19:21

复杂SoC内部有很多具有独立功能的硬件模块,例如CPU cores、GPU cores、USB控制器、MMC控制器、等等,出于功耗、稳定性等方面的考虑,有些SoC在内部为这些硬件模块设计了复位信号(reset signals),软件可通过寄存器(一般1个bit控制1个硬件)控制这些硬件模块的复位状态。

2023-10-16 17:11

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可是设置

2017-02-11 11:53

前一阵一直在忙,所以没有来得及写博文。弄完杂七杂八的事情,又继续FPGA的研究。使用Verilog HDL语言和原理图输入来完成FPGA设计的方法都试验过了,更高级的还有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10

本文是Speos Sensor System(SSS)的使用指南,这是一个强大的解决方案,用于camera sensor模拟结果的后处理。本文的目的是通过一个例子来理解如何正确使用SSS。当然本文描述的分析步骤适合任何案例。

2023-12-03 09:49

stm32每一个GPIO端口拥有2个32bits的configuration寄存器(GPIOx_CRL,GPIOx_CRH),2个32bits的数据寄存器(GPIOx_IDR,GPIOx_ODR

2019-11-01 16:28