它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。

2018-09-03 16:27

在数字电子技术中我们会经常进行高低电平之间的转化,比如说一个模块在接收到信号的时候输出高电平,而另一个元件是低电平触发,如果这两个元器件能够很好配合使用的话,这就必须需要进行电

2022-12-12 09:12

事实上,它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。结合实际讲一个有用的例子来加深印象: 我们有的同学可能已经学习了这样的一条PCB布线

2018-02-06 12:37

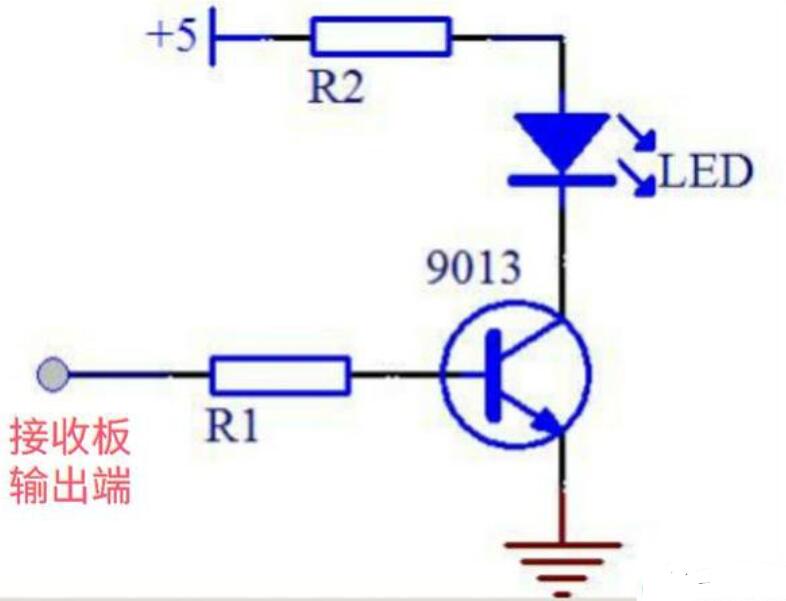

想将一个红外遥控接收板的4个默认输出为低电平的端口改为默认输出为高电平,当接收到红外遥控信号时相应端口输出变为低电平。

2019-11-02 04:00

,断开系统电源,然后再次连接电源以重启系统。本文将探讨使用什么方法和技术可以监控电路的低电平有效输出来驱动高端输入开关,从而执行系统电源循环。

2024-10-30 09:22

FPGA在上电后,会立刻将nSTATUS配置状态管脚置成低电平,并在上电复位(POR)完成之后释放它,将它置为高电平。作为配置状态输出管脚,在配置过程中如果有任何一个错

2019-09-01 10:37

1.CMOS电平: ‘1’逻辑电平电压接近于电源电压,‘0’逻辑电平接近于0V。噪声容限很大 2.TTL电平: 输出高电平

2019-09-14 10:52

导致内核协议栈发送了一个rst报文,而rst报文选取seq的时候,并不是选取的确定已经发送的seq,而是当前连接已经用掉的seq,也就是当前seq,哪怕这个报文没有收到回复,也会使用。

2018-07-27 15:26

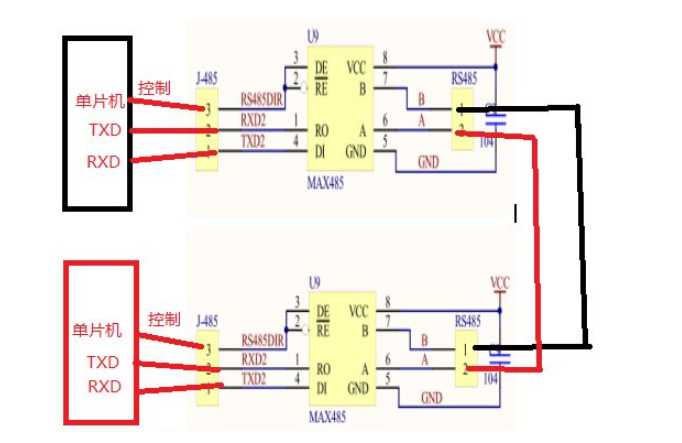

今天给大家分享关于STM32关于UART的一些新特性,主要针对较新系列STM32(如:STM32H7、G0、G4等)的UART,可通过软件改变Rx和Tx引脚、电平反转、

2019-09-08 10:29

ODR寄存器可读可写:既能控制管脚为高电平,也能控制管脚为低电平。 管脚对于位写1 gpio

2018-11-01 15:45