它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。

2018-09-03 16:27

今天给大家分享关于STM32关于UART的一些新特性,主要针对较新系列STM32(如:STM32H7、G0、G4等)的UART,可通过软件改变Rx和Tx引脚、电平反转、

2019-09-08 10:29

芯片设计工程师常常需要根据输入输出信号(Input and Output, I/O)实现管脚电平数字逻辑。例如,系统工程师利用微控制器进行时钟增殖时常常需要创建时钟树,将输入时钟输入至多个缓冲时钟(具有适当的驱动能力),和/或倒转时钟极性。还有许多场景下,系统工程

2018-04-07 10:04

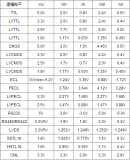

作为一名电子设计的硬件工程师,电平转换是每个人都必须面对的的话题,主芯片引脚使用的1.2V、1.8V、3.3V等,连接外部接口芯片使用的1.8V、3.3V、5V等,由于电平不匹配就必须进行电平转换

2020-03-09 10:40

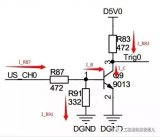

前段时间在设计NB-IOT模块与STM32的硬件通讯时用到了电平转换。当主控芯片引脚电平与外部连接器件电平不匹配的时候就需要用电

2020-11-03 15:50

FPGA在上电后,会立刻将nSTATUS配置状态管脚置成低电平,并在上电复位(POR)完成之后释放它,将它置为高电平。作为配置状态输出

2019-09-01 10:37

高电平,也能控制管脚为低电平。 对寄存器高 16bit 写1 对应管脚

2018-11-01 15:45

输入高电平门限Vih:保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入

2018-03-10 09:47

什么是TTL电平、CMOS电平、RS232电平?它们有什么区别呢?一般说来,CMOS电平比TTL电平有着更高的噪声容限。

2023-02-07 14:58

左端接3.3VCMOS电平,可以是STM32、FPGA等的IO口,右端输出为5V电平,实现3.3V到5V电平的转换。

2018-12-13 16:10