本文给出了采用这些技术的高速环境状态机设计的规范及分析方法和优化方法,并给出了相应的示例。 为了使FPGA或CPLD中的状态机设计

2009-04-15 11:27

状态机的基础知识依然强烈推荐mooc上华科的数字电路与逻辑设计,yyds!但是数电基础一定要和实际应用结合起来,理论才能发挥真正的价值。我们知道FPGA是并行执行的,如果我们想要处理具有前后顺序的事件就需要引入状态机。

2023-07-28 10:02

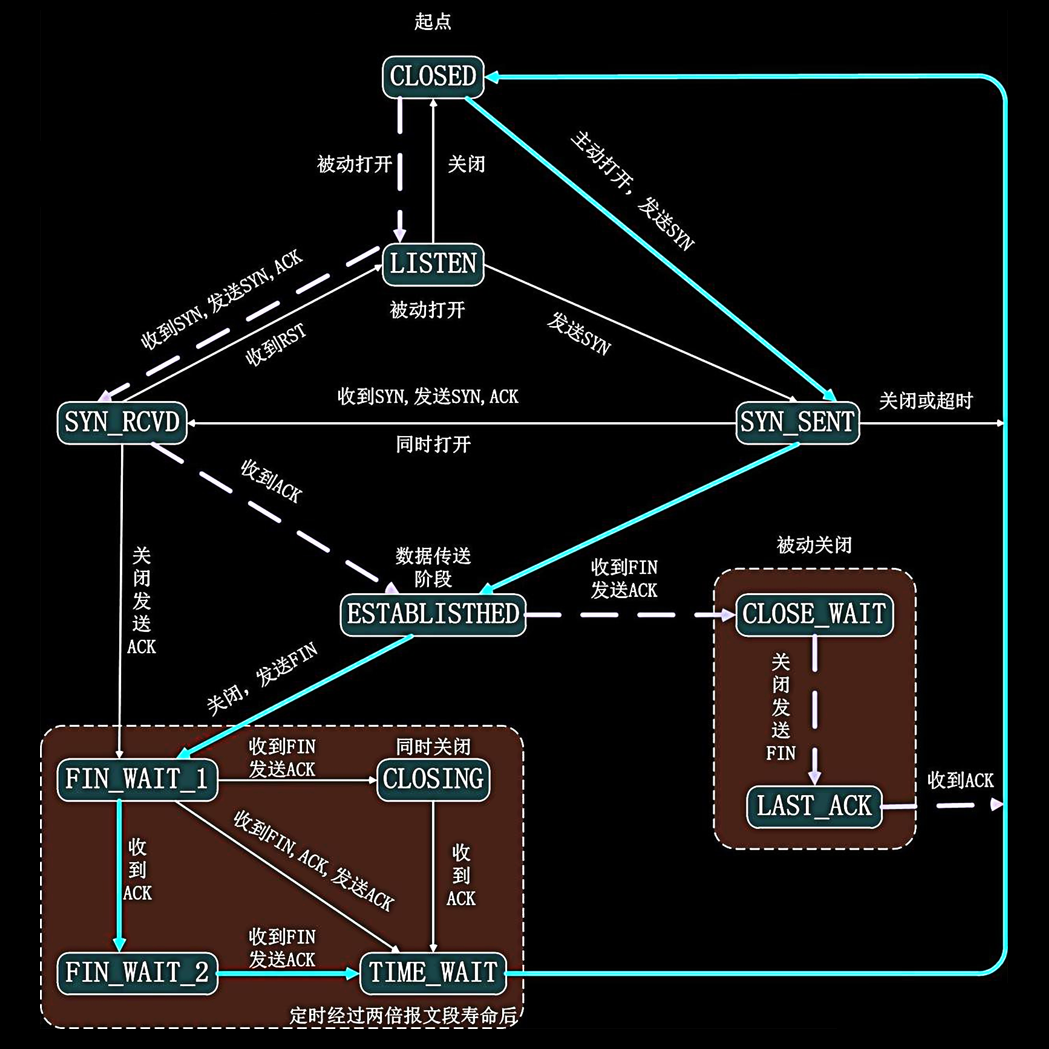

TCP状态机是TCP连接的变化过程。TCP在三次握手和四次挥手的过程,就是一个TCP的状态说明,由于TCP是一个面向连接的,可靠的传输,每一次的传输都会经历连接,传输,关闭的过程,无论是哪个方向的传输,必须建立连接才行,在双方通信的过程中,TCP的

2023-04-21 11:47

状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心。

2019-10-09 07:02

有限状态机设计的关键是如何把一个实际的时序逻辑关系抽象成一个时序逻辑函数,传统的电路图输入法通过直接设计寄存器组来实现各个状态之间的转换, 而用硬件描述语言来描述有限

2011-11-11 09:49

状态机,又称有限状态机(Finite State Machine,FSM)或米利状态机(Mealy Machine),是一种描述系统状态变化的模型。在芯片设计中,

2023-10-19 10:27

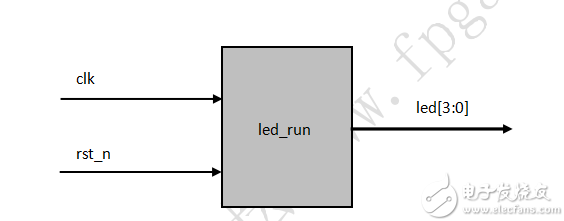

本篇文章包括状态机的基本概述以及通过简单的实例理解状态机

2019-01-02 18:03

设计背景: 状态机是描述各种复杂时序的时序行为,是使用 HDL进行数学逻辑设计中非常重要的方法之一,状态机分为摩尔机和米粒机,当输出只和状态有关系的话称为摩尔机,当输出不仅和状

2018-06-01 16:59

本文目录 前言 状态机简介 状态机分类 Mealy 型状态机 Moore 型状态机 状态机描述 一段式

2020-11-05 17:58

状态机举例 你可以指定状态寄存器和状态机的状态。以下是一个有四种状态的普通状态

2009-03-28 15:18