项目中需要使用CPLD完成一部分算法设计,参数由AVR给出,因此需要完成AVR和CPLD的通信。因此写了一个测试程序。CPLD挂在AVR的数据和地址总线上,AVR使用A

2019-06-03 15:24

STM32 通过 FSMC 读写CPLD 的程序,CPLD挂在STM32的地址线和数据线上,将CPLD看做片外RAM的方

2018-04-20 10:38

本文给出了DSP多SPI端口通信的设计与实现过程,讨论了其中的关键技术问题。SPI多端口通信方法基于CPLD实现,易移植,易于实现功能扩展,可广泛应用于各种采用SPI通信

2011-05-30 11:22

采用CPLD与绝对式编码器进行高速串行通信,CPLD再把收到的编码器信息转变为并行数据传送给伺服单元中的DSP进行运算控制,本文将给出CPLD与绝对式编码器高速串行

2011-08-13 14:57

CPLD内部施密特触发器电器特性见表1。目前大部分使用的CPLD都需要两个电源VCC和VCCIO,VCC就是CPLD内部的核电压,VCCIO是CPLD所有I/O 引脚电

2018-05-11 08:22

都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作种取得事半功倍的效果。

2023-05-18 08:56

FPGA LAB和CPLD的LAB设计不同。CPLD LAB由宏单元构成,包括自己的本地可编程阵列,而FPGA LAB由大量的逻辑模块构成,这些模块被称为逻辑单元,即LE,而且本地互连和逻辑分开。LE看起来可能和CPLD

2018-04-17 17:02

AMD公司最先生产带有宏单元的可编程逻辑器件PAL22V10。目前PAL22V10已成为划分PLD的界限。可编程逻辑器件所包含的门数大于PAL22V10所包含则门数,就被认为是复杂可编程逻辑器件,即CPLD。

2018-05-24 01:39

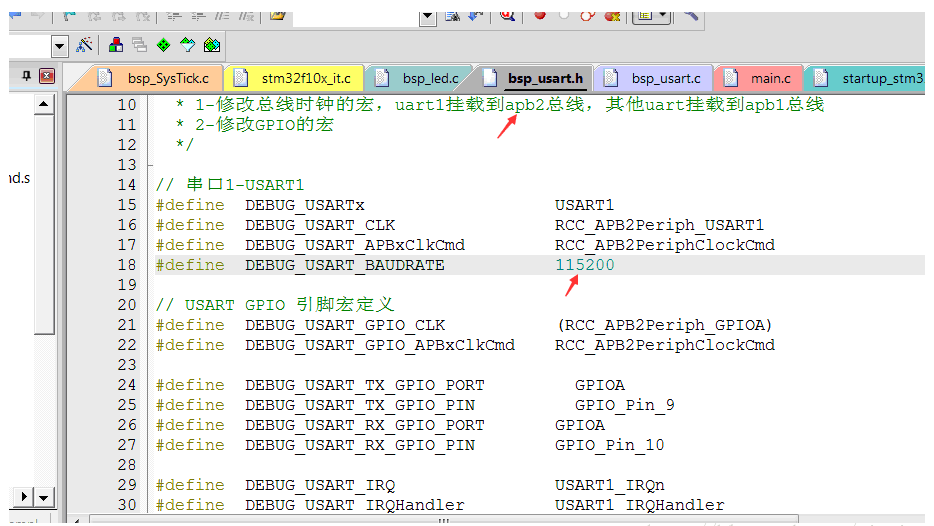

STM32串口通信以及温度采集搞定,其中主要遇到STM32系列单片机时钟树的问题,串口通信遇到串口调试助手能够接收到数据但出现乱码现象,开始一直以为是串口配置和程序代码

2018-06-22 08:01

CPLD和FPGA都是由逻辑阵列模块构成的,但是CPLD的LAB基于乘积和宏单元,而FPGA的LAB使用基于LUT的逻辑单元。CPLD的LAB围绕中心全局互连排列,随着器件中逻辑数量的增加,呈指数

2024-01-23 09:17