使用IAR IDE仿真RL78内置硬件乘法器和除法器注意事项

2023-10-30 17:04

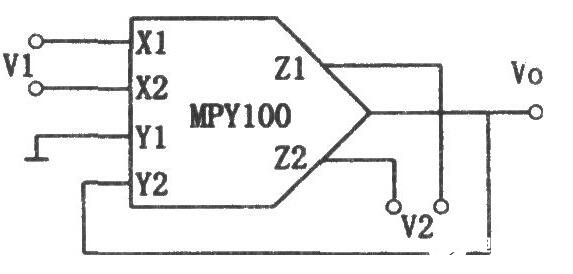

输入信号为V1、V2,输出Vo为Vo=10V2/V1。这种除法器是将乘法器接在运算放大器的反院回路组成的。V1的输入范围为-0.2V到10V,V2的输入范围为-10V到10V。

2019-12-31 14:12

FPGA可以通过除号直接实现除法,但是当除数或被除数位宽较大时,计算会变得缓慢,导致时序约束不能通过。此时可以通过在除法IP中加入流水线来提高最大时钟频率,这种方式提高时钟频率也很有限。如果还不能达到要求,就只能把除法

2025-10-28 14:56

FPGA实现除法的方法有几种,比如直接用/来进行除法运算,调用IP核进行除法运算,但这两种方式都有个共同的问题——都是黑盒子,在进行时序违例处理时,往往不好操作,比如想打打拍改善下时序都不知从何下手。

2023-07-04 10:03

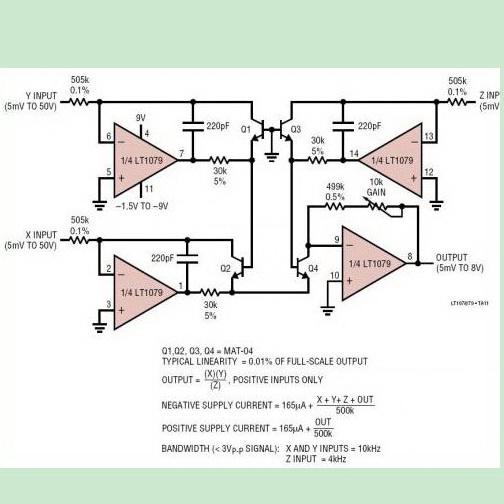

X、Y 和 Z 输入放大器执行伺服操作,以根据施加的信号来控制晶体管的发射极电流。晶体管 Vbe 随电流呈对数变化,因此 Q2 的发射极包括 X 和 Y 对数之和。Z信号对数在 Q4 的基极上提供,于是 Q4 上最终的 Vbe 为 Vbe1 + Vbe2 - Vbe3。

2018-07-05 10:07

NI Multisim 10经典教程分享--除法与开平方运算电路

2023-02-08 09:18

本文在设计实现乘法器时,采用了4-2和5-2混合压缩器对部分积进行压缩,减少了乘法器的延时和资源占 用率;经XilinxISE和QuartusII两种集成开发环境下的综合仿真测试,与用

2018-12-19 13:30

单片机中的除法也是二进制的除法,和现实中数学的除法类似,是从被除数的高位开始,按位对除数进行相处取余的运算,得出的余数再和之后的被除数一起再进行新的相除取余的运算,直到除不尽为止,因为单片机中的

2018-05-31 08:51

除法器是电子技术领域的基础模块,在电子电路设计中得到广泛应用。目前,实现除法器的方法有硬件实现和软件实现两种方法。硬件实现的方法主要是以硬件的消耗为代价,从而有实

2012-05-24 09:41

模拟除法器是一种能实现两个模拟量相除的电子器件。目前不仅应用于模拟运算方面,而且已扩展到无线通讯、电视广播、人工神经网路、机器人控制技术等领域。此外,模拟除法器在模糊控制和测量仪表中也是非常重要的器件。

2014-09-19 15:14