本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的

2023-07-10 10:22

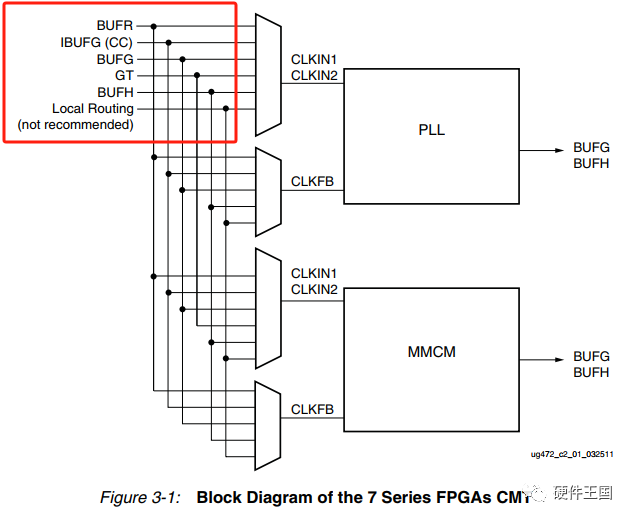

7系列FPGA包含最多24个CMT块,CMT具体的分布和与其他时钟资源的关系请参考本合集(FPGA应用开发)的上一篇文章。本文主要介绍CMT内部MMCM和PLL的区别以及在实际开发中怎么使用CMT,怎么实现跨时钟区域,第一次读者最好先阅读上一篇文章——解剖时钟结构

2023-11-17 17:08

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buffer";

2017-02-09 12:54

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

1,描述 说到复位,我们都不会陌生,系统基本都有一个复位按键。复位的种类有很多:上电复位、掉电复位、复位引脚复位、看门狗复位、软件复位等。本文探讨的就是在stm32中复位电路如何设计。 2

2023-06-22 09:06

PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的

2017-05-22 09:16

下面我们来看本实例如何配置一个PLL硬核IP,并将其集成到工程中。如图8.18所示,在新建的工程中,点击菜单“ToolsàMegaWizard Plug-In Manager”。

2018-04-24 11:30

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短

2018-05-11 15:14

STM32是一款非常强大的微控制器系列,具有丰富的外设和功能。中断是STM32中非常重要的部分,能够帮助我们提高系统的响应速度和效率。本文将详细介绍STM32

2024-01-02 17:35