CASE语句用来选择几个分支程序部分之一。选择是基于选择表达式当前值的。

2020-10-09 09:26

CASE语句用于根据不同的条件执行不同的操作。以下是使用CASE语句的示例: 示例1:根据输入的值执行不同的操作 在示例1中

2023-06-19 09:57

决策语句(Decision statements)允许程序块的执行流程根据设计中信号的当前值分支到特定语句。SystemVerilog有两个主要的决策语句:if…else语句

2023-02-09 14:15

SystemVerilog case语句与C switch语句类似,但有重要区别。SystemVerilog不能使用break语句(C使用break从switch

2022-10-27 08:57

Verilog-2005中有3个generate 语句可以用来很方便地实现重复赋值和例化(generate for)或根据条件选择性地进行编译(generate if和generate case)等功能。接下来就一起

2022-12-28 15:21

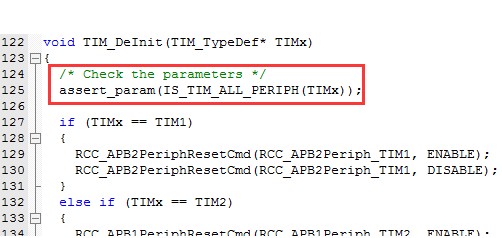

assert_param语句是用于程序开发的时候,调试用的检测语句。默认是不开启的,你可以无视它的存在。但是,当你在调试程序的时候,可以打开这个检测机制,调试完了再关闭。

2018-11-28 16:03

的用法和功能。 一、Assign语句 Assign语句的定义和语法 Assign语句用于在HDL中连续赋值,它允许在设计中

2024-02-22 16:24

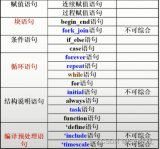

不可综合语句经常用在测试文件中,未注明的语句均是可综合的

2023-07-02 10:47

CASE:创建多路分支 说明 使用“创建多路分支”指令,可以根据表达式的值执行多个指令序列中的一个。 表达式的值必须为整数或位字符串。执行 CASE 指令时,会将表达式(变量)的值与多个常数的值进行

2023-06-27 11:46

令“FOR”、“WHILE”和“REPEAT-UNTIL”的运行:由于系统不显示这些指令中的变量值,因此可避免对循环时间造成影响。 WHILE允许由执行条件控制的循环地执行语句序列。执行条件根据逻辑表达式的规则构成

2023-09-10 09:48