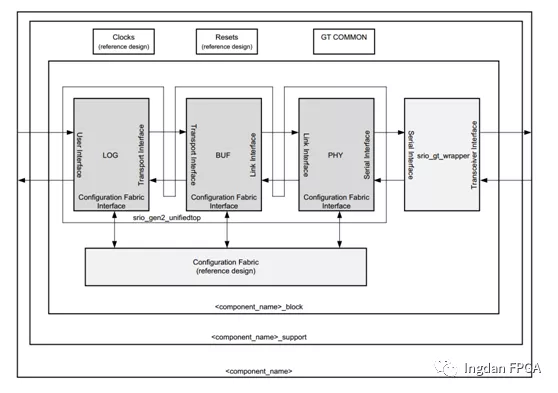

RapidIO标准分为三层:逻辑,传输和物理。

2022-04-12 19:51

随着PCIe接口、以太网接口的飞速发展,以及SOC芯片的层出不穷,芯片间的数据交互带宽大大提升并且正在向片内交互转变;SRIO接口的应用市场在缩小,但是由于DSP和PowerPC中集成了SRIO接口,因此在使用DSP/Power PC + FPGA的使用场景中仍然

2022-08-02 10:00

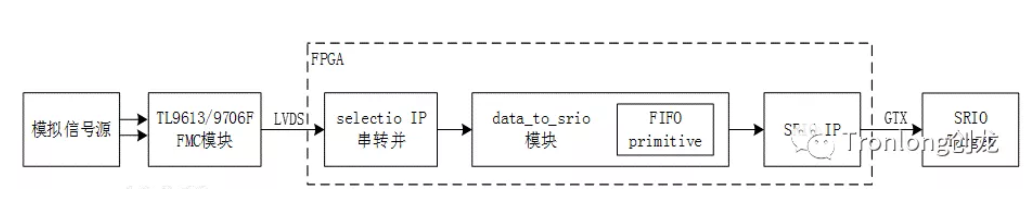

案例说明 1. Kintex-7 FPGA使用SRIO IP核作为Initiator,通过AD9613模块采集AD数据。AD9613采样率为250MSPS,双通道12bit,12bit按照16bit

2020-06-15 18:18

SRIO(Serial RapidIO)交换芯片是一种高性能的通信芯片,专门设计用于实现基于SRIO协议的数据交换和传输。SRIO是一种点对点串行通信协议,广泛应用于嵌入式系统、高性能计算、网络通信

2024-03-16 16:40

在使用FPGA的时候,有些IP核是需要申请后才能使用的,本文介绍如何申请xilinx IP核的license。

2024-10-25 16:48

本文介绍了Vidado中FFT IP核的使用,具体内容为:调用IP核>>配置界面介绍>>IP

2024-11-06 09:51

对于IP核输出数据的解析最好的工具就是其自带的仿真文件,里面既将接收的数据进行了解析,又将发送给IP核的数据进行了封装,这对于了解数据结构和协议是十分有帮助的,以太网如

2018-07-09 14:07

FPGA(现场可编程门阵列)和DSP(数字信号处理器)之间通过SRIO接口进行调试通常需要以下步骤。

2024-04-19 11:48

有些时候,根据设计需求可能会想要修改IP核生成的源文件(只能修改未加密文件),包括HDL文件和XDC约束文件。这种修改不能直接修改源文件,因为在后续设计流程中,IP可能会复位或重新生成,导致修改操作被复原。本文将介绍

2022-08-25 14:38

学完SDRAM控制器后,可以感受到SDRAM的控制器的书写是十分麻烦的,因此在xilinx一些FPGA芯片内已经集成了相应的IP核来控制这些SDRAM,所以熟悉此类IP核

2019-11-10 10:28