本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单

2023-12-12 09:19

SRIO这种高速串口复杂就复杂在它的协议上,三层协议:逻辑层,传输层以及物理层。 数据手册会说这三层协议是干什么的呢?也就是分工(【FPGA】SRIO IP核系统

2023-04-25 11:20

SRIO是面向嵌入式系统开发提出的高可靠、高性能、基于包交换的新一代高速互联技术,已于2004年被国际标准化组织(ISO)和国际电工协会(IEC)批准为ISO/IECDIS 18372标准。SRIO则是面向串行背板、DSP和相关串行数据平面连接应用的串行Rapid

2020-06-17 11:48

数据从远程设备(假设为DSP的SRIO端)传输过来,FPGA端(假设我们这端为FPGA的SRIO端口)通过RX接收到串行数据,先到达物理层进行时钟恢复,串并转换,之后进行8b/10b解码操作、CRC校验,这一系列的操作都在物理层完成,之后进入传输层

2023-03-03 10:19

RapidIO标准分为三层:逻辑,传输和物理。

2022-04-12 19:51

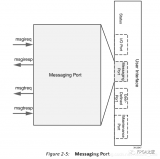

消息传递端口是可选接口(消息也可以组合到I / O端口上,并使用Vivado集成设计环境(IDE)设置视为写入事务)。单独的Messaging端口遵循Initiator / Target样式。

2023-10-10 15:58

本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单

2023-09-04 18:19

两者通信不了,查原因发现fpga srio ip核的 lnk_trdy_n信号不对,但lnk_rrdy_n信号正常,mode-sel正常。 希望得到高人解答。(Serial RapidIO v5.6)

2018-06-21 00:10

现在,我在ISE13.1软件中使用srio_v5_6 Ip内核。我使用CORE生成器为X6VLX240T-1156-1设备生成一个srio_v5_6 IP内核。然后我用

2018-10-08 11:10

IP CORE SRIO 2.1 ENDPOINT ECP3

2023-03-30 12:02