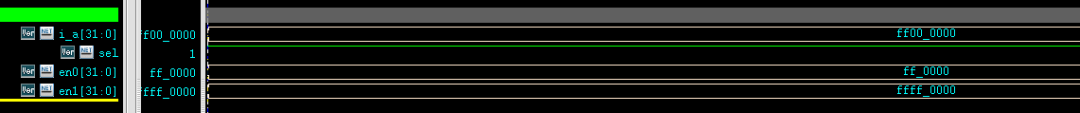

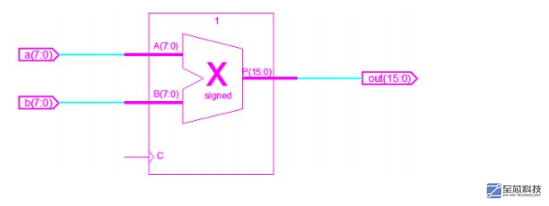

1、在verilog中有时会用signed修饰符来修饰定义的数据,运算的时候也会用$signed()任务来强制转换数据,那么signed的修饰是为什么呢,是为了区分有符号数和无符号数的加法和乘法

2025-02-17 17:47

相信各位小伙伴,都能理解该仿真结果的产生,但是可能有的小伙伴会有疑问,为什么signed_vector的-128结果中间有很多空格?你真的仔细,先为你竖起大拇指,接下来我们就讲解一下为什么输出结果会是这样。

2023-09-02 10:01

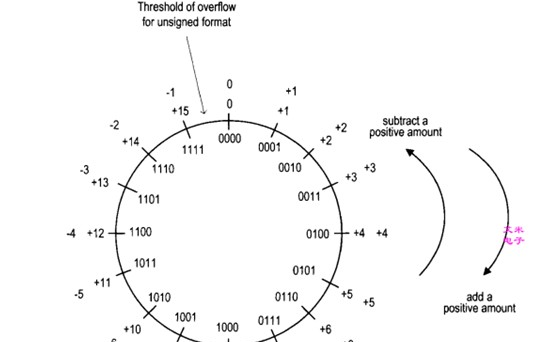

在数字电路中,出于应用的需要,我们可以使用无符号数,即包括0及整数的集合;也可以使用有符号数,即包括0和正负数的集合。在更加复杂的系统中,也许这两种类型的数,我们都会用到。

2020-01-30 09:52

没想到啊没想到啊,有一天会被浓眉大眼的assign背刺!想当年在always消失术里,在X态分析里,在xprop平替策略里,把assign捧的这么高,优点说了800多项,然后今天一仿真出bug了?!

2023-12-04 11:33

Shenzhen, November 7, 2023 - The WLAN Application Ecosystem and Standards forum has concluded successfully during the IEEE Standards Association (SA) General Meeting Anniversaries in Shenzhen, Guangdong, China. This forum gathered experts and industry leaders related to the WLAN industry from worldwide, including the IEEE SA, the IEEE 802.11 Working Group, and the World WLAN Application Alliance (WAA) to jointly discuss the latest advancements in WLAN standards and industries, and to deliberate on how international standards organizations can work closely to promote global trade. Leaders and e

2023-11-09 10:40

C语言各种数据类型的内存映像(32位平台): 0 signed char #include stdio.hint main(){ char min = 17; char max

2022-07-06 14:49

如果一个表达式同时包含signed和unsigned整型,signed会提升为unsgined,可能会隐藏一些意想不到的错误,特别是用在比较运算时

2023-12-28 18:21

C语言各种数据类型的内存映像(32位平台)

2022-06-06 17:01

signed 来处理。 通过“*”运算符完成有符号数的乘法运算。module ceshi (out, clk, a, b); output [15:0] out; input clk; //通过

2018-10-09 15:22

(a, b,c, clk, o); input signed [17:0] a; input signed [17:0] b; input signed [17:0] c; input clk

2024-08-13 11:51