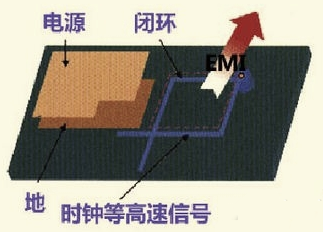

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-05-06 18:08

IIC通信是一种双线制串行总线,由SDA(串行数据线)和SCL(串行时钟线)两条线组成。SDA线用于传输数据,而SCL线则用于传输时钟。在IIC通信中,数据的传输是由主设备发出开始信号,然后将数据发送给从设备,最后发出停止信号结束传输。

2023-08-26 12:02

SDRAM有多种标准,包括DDR(Double Data Rate)、DDR2、DDR3和DDR4。每个标准都具有不同的物理规格和数据传输速率。DDR4是现代计算机中使用的最新型号,它具有更高的频率和更大的容量。

2023-08-26 11:57

电源线尽可能的宽,不应低于18mil,信号线宽不应低于4mil,cpu出入线不应低于4mil(或6mil),线间距不低于8mil;高密度板可采用4/6mil的线宽/间距,低密度版,尽量采用6/8mil的线宽/间距。信号线间距须遵循3W原则。

2019-10-25 14:16

双层pcb板正反两面都有布线,元器件可以焊接在正面,也可以焊接在反面,双层线路板这种电路板的两面都有元器件和布线,不容质疑,设计双层PCB板的难度要高更多,下面我们来分析下双层pcb板布

2017-08-26 16:03

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2017-08-25 15:35

pcb板的厚度是规则设置中的一个重要参数。通常情况下,pcb板的厚度是0.8-3.2mm,厚度的选择取决于电路的复杂性和应用环境。在选择pcb板厚度时,必须考虑到板层的

2023-08-26 12:07

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,则需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。 建议屏蔽线每1000mil打孔接地 。 高速信号的

2023-05-22 09:15

如何优雅的布线呢?布线的方式可以千差万别,为了在布线时避免输入端与输出端的边线相邻平行而产生反射干扰和两相邻布线层互相平行产生寄生耦合等干扰而影响线路的稳定性,甚至在干扰严重时造成电路板根本无法工作,布线时需要考虑诸多因素的影响,现在就给大家安利一下PCB布线的规则

2018-07-28 11:01

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-03-15 14:05