Abstract: This application note describes the JTAG hardware boundary scan chain for the DS26522

2009-04-18 11:45

接着上文,MCU芯片设计了mbist、scan chain之后,功能仿真失败?

2023-02-20 09:35

当然最显而易见的办法就是vclp检查哪儿需要补插isolation cell,那么是否需要补插scan chain的isolation cell, 怎么插呢?

2023-05-10 09:18

模拟到数字的信号不可控,需要和数字registered outputs mux一下提高test coverage。关键词是registered output! 这个技巧俗称scan loopback。

2023-12-08 11:24

2023-08-12 07:24

Abstract: This application note describes the JTAG hardware boundary scan functions of the quad

2009-04-20 09:12

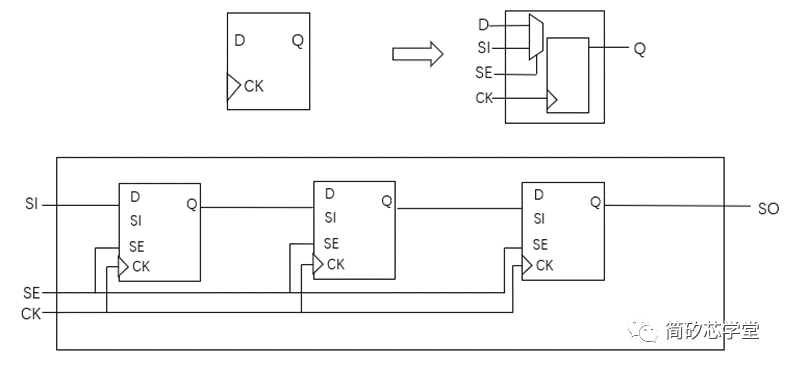

今天这期小编将继续与大家一起学习DFT的相关知识和流程代码,在开始之前,先解决一下上期DFT学习的章节最后留下的问题—DFT工程师在收敛时序timing的时候经常遇到的hold的问题,即不同时钟域的两个SDFF(扫描单元的SI端hold违例问题。

2023-04-16 11:34

随着现代集成电路工艺的发展,芯片制成越来越来精密,出现缺陷的可能性也越来越高,有时候一个微不足道的影响就可能导致芯片报废

2023-09-15 11:29

由于增加了大量的mux来完成时钟、复位可控,导致中端网标中的cell有工艺库文件指定的delay参数,默认是1ns,那么会造成clk delay,比如插入两级mux就会形成2ns延时

2023-02-19 10:11

使用蜂鸟官方的调试器和正点原子7a100t芯片的fpga开发板进行蜂鸟开源e203核心移植,硬件下载没问题,管脚绑定也没问题,连线也检查了多次。 但是使用nucleistudio——202212版本按官方教程进行下载还是出现了openocd报错,报错信息如下。 论坛看了,发现很多人都有这个问题但都没有解决。

2024-05-17 15:45