PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走

2019-10-04 17:17

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

2019-12-16 14:52

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,则需要进行屏蔽处理,如果

2023-05-22 09:15

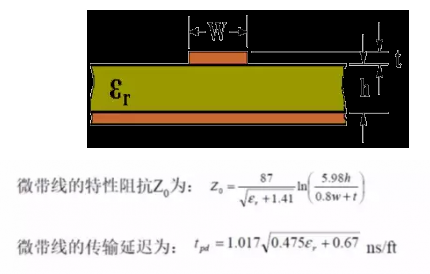

传输线的定义是有信号回流的信号线(由两条一定长度导线组成,一条是信号传播路径,另一条是信号返回路径),最常见的传输

2020-11-06 10:25

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建

2019-03-15 14:05

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走

2019-10-13 13:19

Analog Discovery信号线组件,或称Flywire,是与Analog Discovery产品原装信号线相同的组件。

2019-11-26 11:08

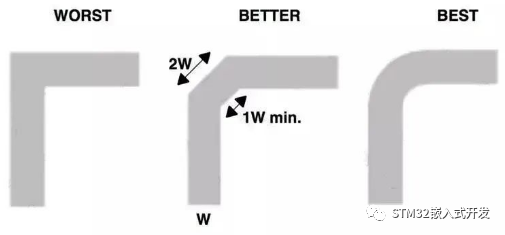

现在但凡打开SoC原厂的PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直

2023-04-03 16:29

高扇出信号线 (HFN) 是具有大量负载的信号线。作为用户,您可能遇到过高扇出信号线相关问题,因为将所有负载都连接到 HFN 的驱动程序需要使用大量布线资源,并有可能导致布线拥塞。鉴于负载分散,导致进一步增大

2025-08-28 10:45

一根线为正极性信号线(P线),另一根线为负极性信号线(N线),这两根

2024-05-16 16:33