SystemVerilog能够在许多不同的细节级别(称为“抽象级别”)对数字逻辑进行建模。抽象意味着缺乏细节。数字模型越抽象,它所代表的硬件的细节就越少。

2023-02-09 14:20

对于前端设计人员,经常会需要一个MUX来对工作模式,数据路径进行明确(explicit)的声明,这个对于中后端工程师下约束也很重要。这里介绍一种巧用的RTL原语,实现MUX的方法。

2023-12-14 16:26

ModelSim是工业界最优秀的语言仿真器,它提供最友好的调试环境,是作FPGA、ASIC设计的RTL级和门级电路

2019-11-19 14:54

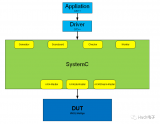

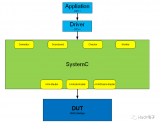

当FPGA开发者需要做RTL和C/C++联合仿真的时候,一些常用的方法包括使用MicroBlaze软核,或者使用QEMU仿真ZYNQ的PS部分。

2023-12-13 10:13

当FPGA开发者需要做RTL和C/C++联合仿真的时候,一些常用的方法包括使用MicroBlaze软核,或者使用QEMU仿真ZYNQ的PS部分。

2023-12-13 10:11

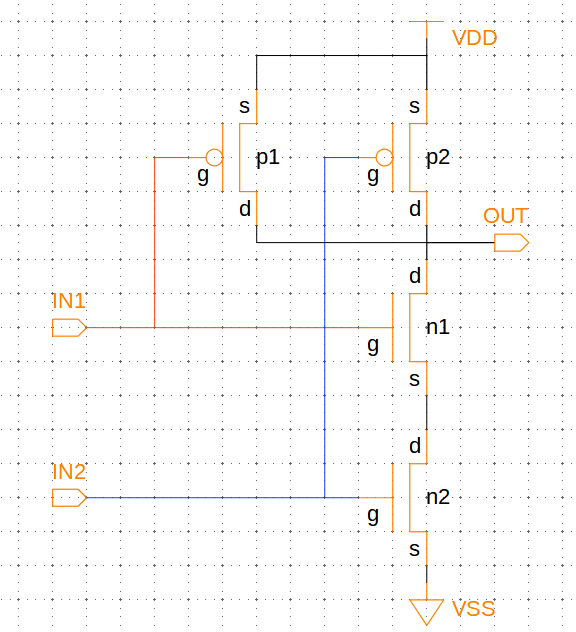

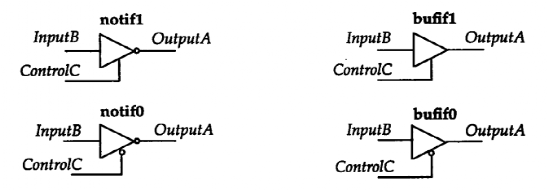

标准单元库是数字集成电路的积木,是复杂电路和系统的基础。今天我们来认识一下其中的几个常用门级电路。

2023-10-09 15:49

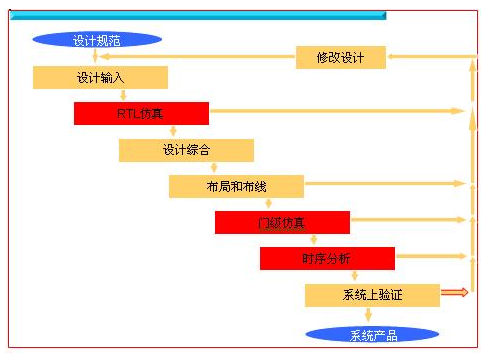

数字电路设计中一般包括3个大的阶段:源代码输入、综合和实现,而电路仿真的切入点也基本与这些阶段相吻合,根据适用的设计阶段的不同仿真可以分为RTL行为级

2018-07-02 08:43

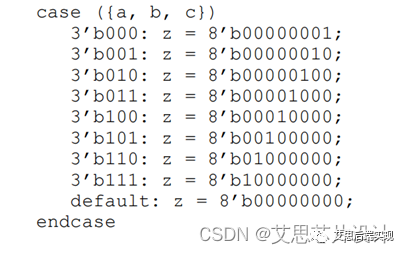

综合成基本的门级电路网络,但对于复杂的设计来说,行为级建模的效率远远高于门级建模。所以目前 Verilog 大多数用于描

2023-03-30 11:35

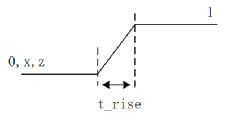

前两节中所介绍的门级电路都是没有延迟的,实际门级电路都是有延迟的。

2023-03-30 11:31