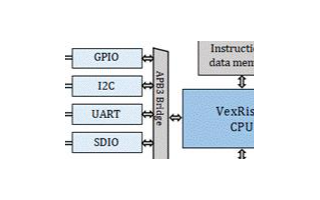

整个RISC-V片上系统设计如图1所示。该系统主要由RISC-V软核CPU、指令/数据存储器、总线桥、外围设备、DMA(直接存储器访问)和卷积加速器组成。

2022-11-18 11:04

本帖最后由 我爱下载 于 2022-4-8 18:23 编辑 测试RISC-V的软核处理器以下测试采用官方提供的picotiny例程完成PicoRV32处理器的测试,测试包括串口、GPIO

2022-03-19 14:33

Microsemi 于 2017 年开始在其 FPGA 中提供 RISC-V 软核,Lattice 于 2020 年开始提供,英特尔 (Altera) 于 2021 年开始提供,因此 Xilinx

2024-11-11 10:24

单元(LUT4/LUT5混合架构),130KB SRAM,32bit 位宽64MBit SDRAM,用来跑 RISC-V 的软核相当合适了。 为了给这块 FPGA 烧录 bitstream 把它变成

2022-09-16 16:15

64MBit SDRAM,丰富的LVDS引脚,内置12-bit 1MSPS ADC ,这为荔枝糖提供了无限的可能性:FPGA可以模拟“HummingbirdE200/E203 RISC-V软核”来帮助

2018-10-18 14:02

的【RISC-V专题】 开发板 试用活动,一次性推出了17款各种类型的开发板型——主控芯片涉及低功耗MCU、通用型MCU、高性能MCU、AI专用MCU,以及带有MMU的SoC,还有可用于RISC-V软

2022-11-15 15:08

SIPEED LONGAN NANO - RISC-V GD32

2024-03-14 22:29

GAPUINO GAP8 RISC-V DEV KIT

2024-03-14 22:29

,用于配备轻量级RISC-V软核的国产FPGA(紫光同创PG2L100H)。所提出的加速器的峰值性能达到153.6 GOP/s,仅占用14K LUT(查找表)、32个DRM(专用RAM模块)和208个APM(算术处理

2023-08-21 10:30

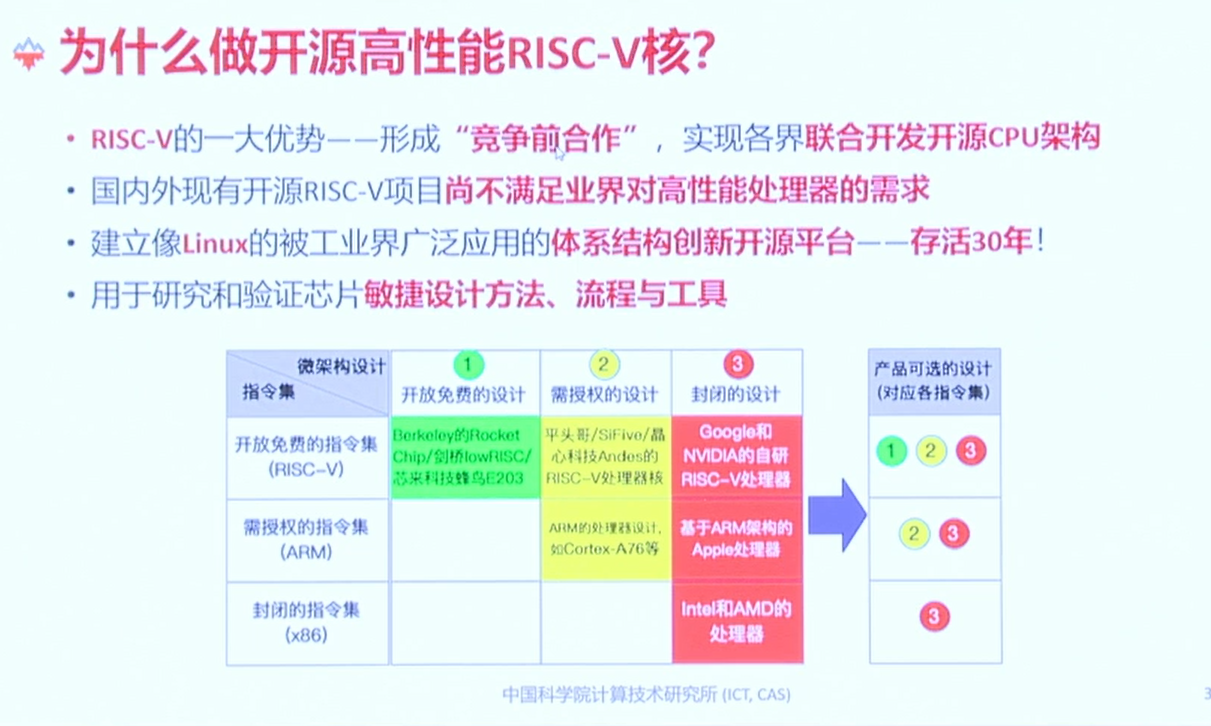

RISC-V是一个基于精简指令集原则的开源指令集架构,那么为什么做开源高性能RISC-v核?

2021-06-22 14:25