整个RISC-V片上系统设计如图1所示。该系统主要由RISC-V软核CPU、指令/数据存储器、总线桥、外围设备、DMA(直接存储器访问)和卷积加速器组成。

2022-11-18 11:04

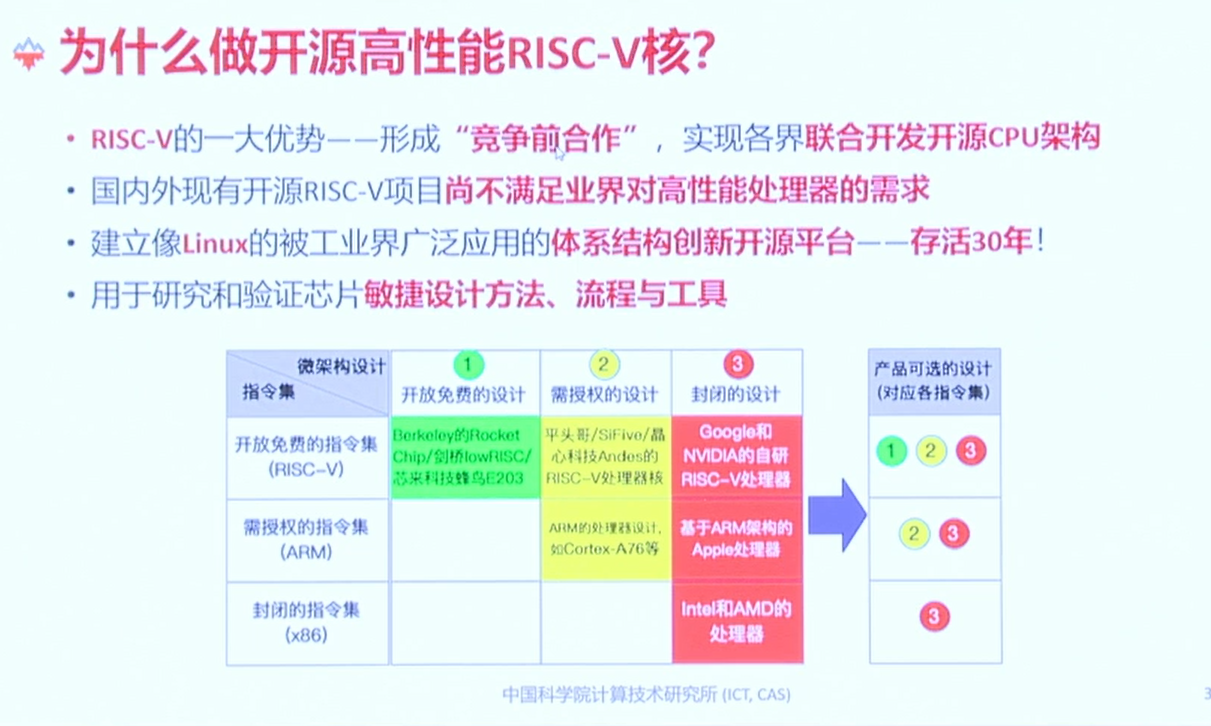

RISC-V是一个基于精简指令集原则的开源指令集架构,那么为什么做开源高性能RISC-v核?

2021-06-22 14:25

,海外巨头在芯片产品端基本垄断市场。MCU的市场特点与RISC-V的技术架构特点相契合,尤其在大量应用ARMIP核的32位以上MCU产品具有较强成本优势,存在替代机会。

2023-04-03 15:29

本期文章目录一个小型RISC-V开源处理器核介绍!#SOC#FPGA#RISC-V点击阅读数字积木从零开始写RISC-V处理器(超详细)#

2021-07-23 09:42

Microsemi 于 2017 年开始在其 FPGA 中提供 RISC-V 软核,Lattice 于 2020 年开始提供,英特尔 (Altera) 于 2021 年开始提供,因此 Xilinx

2024-11-11 10:24

(1)、芯片设计者可选择RISC-V 核 和SoC 平台 构建自己的芯片。比如,使用 PULPino 平台开发 SoC 芯片,内核使用 RI5CY和Zero-risky,国内企业和高校研究项目都有在

2023-06-21 20:34

的应用,因此他们正努力研发RISC-V内核,最新的SOC产品小核就应用了RISC-V架构,后续推出的产品大小

2022-04-13 17:31

的 RISC-V 计算平台,促进形成贯穿 IP 核、芯片、软件、系统、应用等环节的 RISC-V 产业生态链。中国联通指出,RISC-V 是基于精简指令集计算(

2023-03-16 14:56

。例如,如果工程师在FPGA中实现软RISC-V内核,则通常可以使用RTL源代码。由于RISC-V免版税,这为将基于RISC-V的设计从FPGA移植到ASIC或另一个F

2020-07-27 17:38

主题演讲:RISC-V和RISC-V AI的未来(特邀讲座)ppt分享

2023-07-14 17:15