《UltraFast 设计方法时序收敛快捷参考指南》提供了以下分步骤流程, 用于根据《UltraFast设计方法指南》( UG949 )中的建议快速完成时序收敛: 1初

2021-11-05 15:10

更快,而一个坏的代码风格则给后续时序收敛造成很大负担。你可能要花费很长时间去优化时序,保证时序收敛。拆解你的代码,添加寄

2020-11-20 15:51

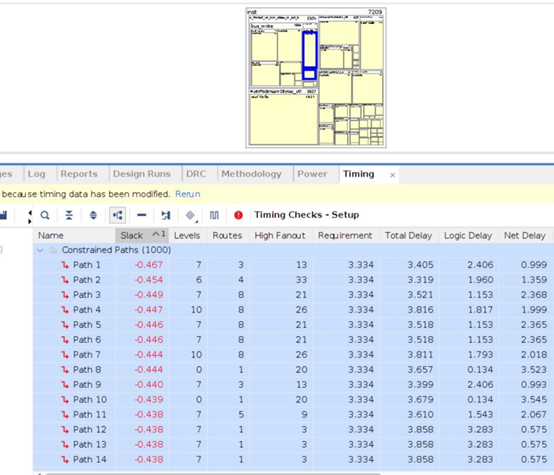

在之前的文章里面介绍了Canny算法的原理和基于Python的参考模型,之后呢在FPGA上完成了Canny算法的实现,可是遇到了时序不收敛的问题,记录一下。

2023-11-18 16:38

FPGA时序不收敛,会出现很多随机性问题,上板测试大概率各种跑飞,而且不好调试定位原因,所以在上板测试前,先优化时序,再上板。

2023-06-26 15:41

本文旨在提供一种方法,以帮助设计师判断给定模块是否能够在空裸片上达成时序收敛。 如果目标模块无法在空裸片上达成非关联 (OOC) 时序收敛,则恐难以与设计其余部分达成

2022-08-02 11:37

如今的集成电路(Integrated Circuit,IC)设计往往要求芯片包含多个工作模式,并且在不同工艺角(corner)下能正常工作。工艺角和工作模式的增加,无疑使时序收敛面临极大挑战。本文

2018-08-05 10:26

更高速的 ADC 在转换器输出和接收机输入之间有严格的时序要求;知道如何利用产品说明书数字来保证无错误数字传输。 最近几年,高速、高精度的模数转换器 (ADC)

2010-07-13 09:59

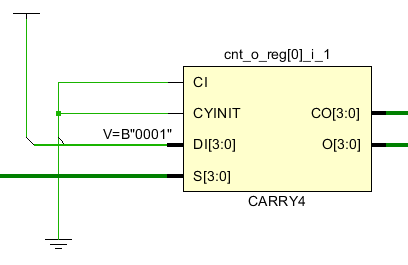

FPGA设计中的绝大部分电路为同步时序电路,其基本模型为“寄存器+组合逻辑+寄存器”。同步意味着时序路径上的所有寄存器在时钟信号的驱动下步调一致地运作。

2023-08-03 09:27

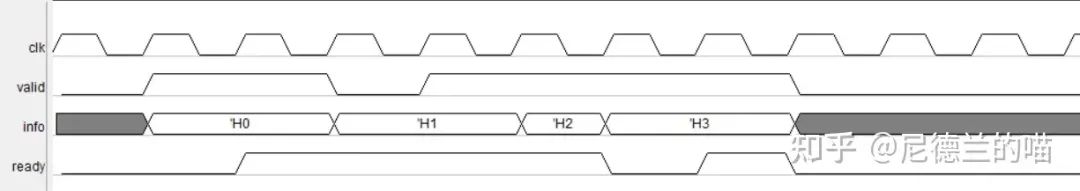

"Valid-Ready" 握手协议是一种常用于数字电路中的接口协议,用于控制数据的传输和处理。

2023-12-04 10:37

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序

2017-11-17 07:54