在之前的文章里面介绍了Canny算法的原理和基于Python的参考模型,之后呢在FPGA上完成了Canny算法的实现,可是遇到了时序不收敛的问题,记录一下。

2023-11-18 16:38

如今的集成电路(Integrated Circuit,IC)设计往往要求芯片包含多个工作模式,并且在不同工艺角(corner)下能正常工作。工艺角和工作模式的增加,无疑使时序收敛面临极大挑战。本文

2018-08-05 10:26

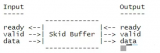

skid buffer(pipeline缓冲器)介绍 解决ready/valid两路握手的时序困难,使路径流水线化。 只关心valid时序参考这篇写得很好的博客链接: 握手协议(pvld

2025-03-08 17:10

生成时序报告后,如何阅读时序报告并从时序报告中发现导致时序违例的潜在问题是关键。 首先要看Design Timing Summary在这个Summary里,呈现了Se

2020-08-31 13:49

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加

2022-08-02 09:25

这篇文章是探讨对接收端进行时序优化(即ready打拍,或称backward打拍)的方式。

2023-12-04 10:20

FPGA器件的需求取决于系统和上下游(upstream and downstrem)设备。我们的设计需要和其他的devices进行数据的交互,其他的devices可能是FPGA外部的芯片,可能是FPGA内部的硬核。

2018-07-11 09:37

介绍了实现网络快速收敛的相关协议以及引起收敛的原因,IXIA正在申请专利的集成在IxNetwork产品中TrueView网络收敛时间测试技术和传统技术的差异。 1 引言 收敛

2018-02-14 09:24

生成时序报告后,如何阅读时序报告并从时序报告中发现导致时序违例的潜在问题是关键。 首先要看Design Timing Summary在这个Summary里,呈现了Se

2020-08-31 13:52

拉氏变换和z变换中,收敛域都是一个重要的概念。这也是复频域分析与频域相比增加的一个内容。为什么有收敛域的问题呢?是因为我们要处理无限长信号,所以,变换公式中积分/求和限是无限的,就有一个是否收敛的问题。如果信号都是有

2018-09-01 10:25